# IEEE O

The magazine for chip and silicon systems designers

IEEE **(**computer society

www.computer.org/micro

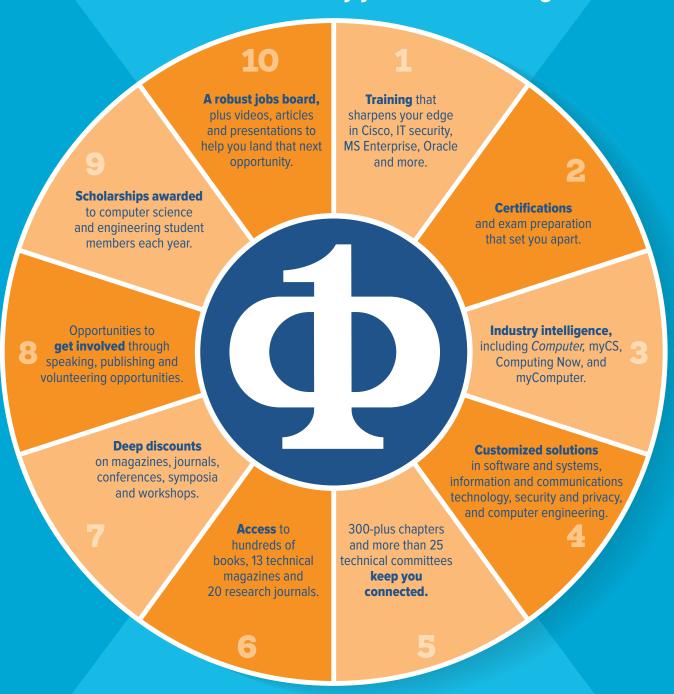

### New Membership **Options for a Better Fit**

And a better match for your career goals. Now **IEEE Computer Society** lets you choose your membership — and the benefits it provides — to fit your specific career needs. With four professional membership categories and one student package, you can select the precise industry resources, offered exclusively through the Computer Society, that will help you achieve your goals.

Learn more at www.computer.org/membership.

## Achieve your career goals with the fit that's right for you.

Explore your options below.

| Preferred I                                                                        | Select your                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| \$60 \$<br>IEEE AJ<br>Member Me                                                    | membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| issues)*                                                                           | Computer magazine (12 digital issues)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ssues)                                                                             | ComputingEdge magazine (12 issues)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                    | Members-only discounts on conferences and events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                                    | Members-only webinars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Now,                                                                               | Unlimited access to <i>Computing Now</i> , computer.org, and the new mobile-ready myCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                                    | Local chapter membership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| urses,                                                                             | Skillsoft's Skillchoice™ Complete with 67,000+ books, videos, courses, practice exams and mentorship resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                    | Books24x7 on-demand access to 15,00 technical and business resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <b>S</b>                                                                           | Two complimentary Computer<br>Society magazine subscriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 30 toker                                                                           | myComputer mobile app                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ry 12 FRE.<br>downloa                                                              | Computer Society Digital Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3 FREE<br>webinar                                                                  | Training webinars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| er                                                                                 | Priority registration to Computer<br>Society events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                                    | Right to vote and hold office                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| .y                                                                                 | One-time 20% Computer Society online store discount                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Now,  ette curses,  to 15,000 es  30 toker  ry  12 FRE downloa  3 FREE webinar  er | ComputingEdge magazine (12 issues)  Members-only discounts on conferences and events  Members-only webinars  Unlimited access to Computing Now, computer.org, and the new mobile-ready myCS  Local chapter membership  Skillsoft's Skillchoice™ Complete with 67,000+ books, videos, courses, practice exams and mentorship resources  Books24x7 on-demand access to 15,00 technical and business resources  Two complimentary Computer Society magazine subscriptions myComputer mobile app  Computer Society Digital Library  Training webinars  Priority registration to Computer Society events  Right to vote and hold office  One-time 20% Computer Society |  |

<sup>\*</sup> Print publications are available for an additional fee. See catalog for details.

### Published by the IEEE Computer Society www.computer.org/micro

November/December 2017 • Volume 37 Number 6

### **Editor in Chief**

Lieven Eeckhout **Ghent University**

### **Editorial Board**

David Brooks, Harvard University Alper Buyuktosunoglu, IBM Bronis de Supinski, Lawrence Livermore National Laboratory Babak Falsafi, EPFL Shane Greenstein, Harvard University Natalie Enright Jerger, University of Toronto Lizy Kurian John, University of Texas at Austin Hyesoon Kim, Georgia Institute of Technology

### John Kim, KAIST

Hsien-Hsin (Sean) Lee, Taiwan Semiconductor

Manufacturing Company Richard Mateosian

Trevor Mudge, University of Michigan, Ann Arbor

Shubu Mukherjee, Cavium Networks

Onur Mutlu, ETH Zurich

Toshio Nakatani, IBM Research

Vojin G. Oklobdzija, University of California, Davis

### Ronny Ronen

Kevin W. Rudd, Laboratory for Physical Sciences

André Seznec, INRIA

Per Stenström, Chalmers University

of Technology

Richard H. Stern, George Washington University

Law School

Lixin Zhang, Chinese Academy of Sciences

### **Advisory Board**

David H. Albonesi, Erik R. Altman, Pradip Bose, Kemal Ebcioglu, Michael Flynn, Ruby B. Lee, Yale Patt, James E. Smith, Marc Tremblay

### **Editorial Staff**

Cathy Martin, cathy.martin@computer.org Editorial Product Lead Molly Gamborg Editorial Management micro-ma@computer.org **Publications Coordinator** Evan Butterfield

Robin Baldwin Senior Manager, Editorial Services Brian Brannon Manager, Editorial Services Debbie Sims, dsims@computer.org

Senior Advertising Coordinator

### CS Magazine Operations Committee

George K. Thiruvathukal (Chair), Gul Agha, M. Brian Blake, Jim X. Chen, Maria Ebling, Lieven Eeckhout, Miguel Encarnação, Nathan Ensmenger, Sumi Helal, San Murugesan, Yong Rui, Ahmad-Reza Sadeghi, Diomidis Spinellis, VS Subrahmanian, Mazin Yousif

### **CS Publications Board**

Director, Products & Services

Greg Byrd (VP for Publications), Alfredo Benso, Irena Bojanova, Robert Dupuis, David S. Ebert, Davide Falessi, Vladimir Getov, José Martínez, Forrest Shull, George K. Thiruvathukal

### **Editorial Office**

10662 Los Vagueros Circle Los Alamitos, CA 90720 +1 714 821-8380

### **Submissions**

https://mc.manuscriptcentral.com /micro-cs

Cover art by Oliver Burston, Début Art

spookypooka@virginmedia.com

For more information on computing topics, visit the Computer Society Digital Library at www.computer.org/csdl.

IEEE Micro (ISSN 0272-1732) is published bimonthly by the IEEE Computer Society. IEEE Headquarters, Three Park Ave., 17th Floor, New York, NY 10016-5997; IEEE Computer Society Headquarters, 2001 L St., Ste. 700, Washington, DC 20036; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, PO Box 3014, Los Alamitos, CA 90720.

Postmaster: Send address changes and undelivered copies to IEEE, Membership Processing Dept., 445 Hoes Ln., Piscataway, NJ 08855. Periodicals postage is paid at New York, NY, and at additional mailing offices. Canadian GST #125634188. Canada Post Corp. (Canadian distribution) Publications Mail Agreement #40013885. Return undeliverable Canadian addresses to 4960-2 Wa<mark>lker Road; Windsor, ON N9A 6J3. Print</mark>ed in USA. Reuse rights and reprint permissions: Educational or personal use of this material is permitted without fee, provided such use: 1) is not made for profit; 2) includes this notice and a full citation to the original work on the first page of the copy; and 3) does not imply IEEE endorsement of any third-party products or services. Author and their companies are permitted to post the accepted version of IEEE-copyrighted material on their own webservers without permission, provided that the IEEE copyright notice and a full citation to the original work appear on the first screen of the posted copy. An accepted manuscript is a version which has been revised by the author to incorporate review suggestions, but not the published version with copy-editing, proofreading, and formatting added by IEEE. For more information, please go to www.ieee.org/publications\_standards/publications/rights/paper versionpolicy.html. Permission to reprint/republish this material for commercial, advertising, or promotional purposes or for creating new collective works for resale or redistribution must be obtained from IEEE by writing to the IEEE Intellectual Property Rights Office, 445 Hoes Lane, Piscataway, NJ 08854-4141 or pubs-permissions@ieee.org. ©2017 by IEEE. All rights reserved. Abstracting

and library use: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy for private use of patrons, provided the per-copy fee indicated in the code at the bottom of the first page is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. Editorial: Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in IEEE Micro does not necessarily constitute an endorsement by IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space. IEEE prohibits discrimination, harassment, and bullying. For more information, visit www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

### **Features**

### **Ultra-Low-Power Processors**

16 Guest Editors' Introduction: Ultra-Low-Power Processors

David Brooks and John Sartori

20 CMOS Scaling Trends and Beyond

Mark T. Bohr and Ian A. Young

30 Low-Power Convolutional Neural Network Processor for a Face-Recognition System

Kyeongryeol Bong, Sungpill Choi, Changhyeon Kim, and Hoi-Jun Yoo

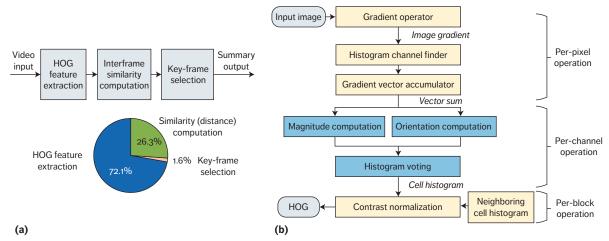

40 Flying IoT: Toward Low-Power Vision in the Sky

Hasan Genc, Yazhou Zu, Ting-Wu Chin, Matthew Halpern, and Vijay Janapa Reddi

52 Visual IoT: Ultra-Low-Power Processing Architectures and Implications

Vui Seng Chua, Julio Zamora Esquivel, Anindya S. Paul, Thawee Techathamnukool, Carlos Flores Fajardo, Nilesh Jain, Omesh Tickoo, and Ravi Iyer

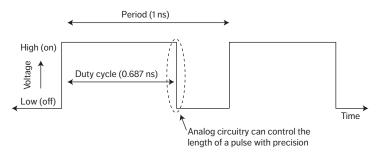

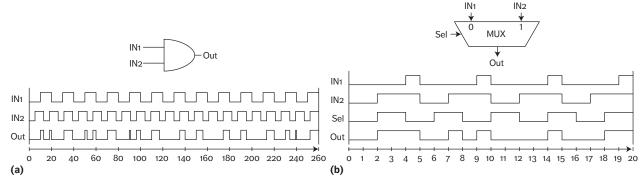

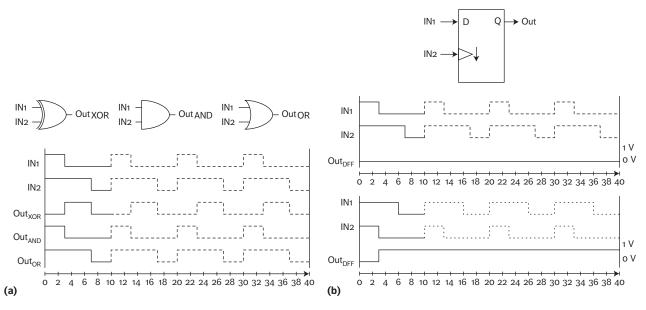

62 An Overview of Time-Based Computing with Stochastic Constructs

M. Hassan Najafi, Shiva Jamali-Zavareh, David J. Lilja, Marc D. Riedel, Kia Bazargan, and Ramesh Harjani

72 Hardware Designs for Security in Ultra-Low-Power IoT Systems: An Overview and Survey

Kaiyuan Yang, David Blaauw, and Dennis Sylvester

### **Departments**

4 From the Editor in Chief

Moore's Law and Ultra-Low-Power Processors

Lieven Eeckhout

**6** Expert Opinion

If You Build It, Will They Come?

Srilatha Manne, Bryan Chin, and Steven K. Reinhardt

**13** Expert Opinion

Blurring the Lines between Memory and Computation Reetuparna Das

90 Awards

2017 International Symposium on Computer Architecture Influential Paper Award David Brooks

92 Micro Economics

The Hush-Hush Norm

Shane Greenstein

### Also in This Issue

5 Computer Society Information

### Moore's Law and Ultra-Low-Power Processors

**Lieven Eeckhout** *Ghent University*

**Welcome to the November/December** 2017 special issue on ultra-low-power processors.

The Internet of Things (IoT) revolution is happening at a rapid pace. Most projections forecast that the number of connected IoT devices will grow exponentially, easily reaching over 100 billion within the next decade. This revolution leads to a vigorous demand for ultra-low-power (ULP) edge computing devices and associated system-on-chip (SoC) architectures. This special issue includes six articles that highlight some of the state-of-the-art research and potentially viable solutions in ULP processors. I suggest you read the guest editors' column for more details about these articles. I want to wholeheartedly thank David Brooks and John Sartori for their excellent work as guest editors of this special issue. I hope you will enjoy reading these articles as much as I did.

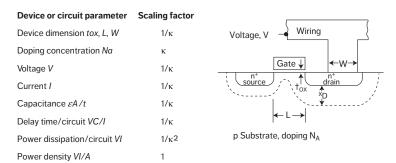

There is one article that I would like to highlight here. Mark Bohr and Ian Young talk about CMOS scaling trends and how Intel has been able to keep Moore's law alive over the past decades. This required continuous innovation in materials and device structures to deliver the performance, power, and cost improvements as expected with each technology generation. The article also highlights new

device options and technology directions to continue scaling in the near future. The excellent keynote Mark delivered at the ISCA 2017 conference instigated this article, and I'm grateful to Mark and Ian for having taken the time to write up this excellent contribution.

This issue also includes two thought-provoking Expert Opinion articles about challenging topics in our field. In the first column, Bobbie Manne, Bryan Chin, and Steve Reinhardt posit that architects should pursue architectural agility to lower the barriers to developing innovative and disruptive solutions in an unpredictable and rapidly evolving technology landscape as we face new technology limitations. They present several ideas for engineers to integrate agility into both processor and datacenter design.

Reetu Das describes two historical waves in processing in memory (PIM) to combat the memory wall, and then argues for moving computation closer to memory—thereby transforming memory into powerful accelerators—which seems like an appealing and promising vision in an era increasingly dominated by data-intensive workloads.

This issue also includes an award testimonial. David Brooks reports on

the 2017 ISCA Influential Paper Award, which was given to "Drowsy Caches: Simple Techniques for Reducing Leakage Power" by Krisztián Flautner, Nam Sung Kim, Steven M. Martin, David Blaauw, and Trevor N. Mudge. This award recognizes the paper published 15 years ago—in this case, 2002—at the ISCA conference that has had the most impact on the field (in terms of research, development, products, or ideas) during the intervening years. The drowsy cache paper made a seminal contribution to power-efficient computing. The paper was written at a time when leakage current was becoming a major concern, especially in large on-chip caches in high-end processors. The paper's key idea was to put parts of the cache into a low-power "drowsy" mode to save energy while retaining the data. Congratulations to the award winners on their groundbreaking research!

Finally, in this issue, Shane Greenstein talks about the "hush-hush norm," which I will let you discover for yourself in the Micro Economics column.

The IEEE Computer Society will be making some changes to how magazine articles are edited. Unfortunately, this means that our current copy editor, Molly Gamborg, will no longer be working with IEEE Micro. Molly has been IEEE Micro's copy editor for seven years. I have interacted with her for many years, first as an author and then as the editor in chief for the past three years. I'm sure that many of you have interacted with Molly as well over these many years, as an author or otherwise. Simply said, Molly did an outstanding job, both in terms of copy editing magazine articles and in terms of managing deadlines and schedules for the magazine. I've always been amazed by her performance and professionalism. She really made my job as the editor in chief easy and enjoyable. I feel very fortunate to have worked with Molly. At the same time, I feel saddened that she will no longer be part of the team. Thanks a lot, Molly, for your great service—we will miss you!

With that, I'd like to conclude and wish you a happy reading.

**Lieven Eeckhout** is a professor in the Department of Electronics and Information Systems at Ghent University. Contact him at lieven.eeckhout@ugent.be.

### Read your subscriptions through the myCS publications portal at http://mycs.computer.org

### IEEE @computer society

**PURPOSE:** The IEEE Computer Society is the world's largest association of computing professionals and is the leading provider of technical information in the field. **MEMBERSHIP:** Members receive the monthly magazine *Computer,* discounts, and opportunities to serve (all activities are led by volunteer members). Membership is open to all IEEE members, affiliate society members, and others interested in the computer field.

OMBUDSMAN: Email ombudsman@computer.org.

COMPUTER SOCIETY WEBSITE: www.computer.org

Next Board Meeting: 12-13 November 2017, Phoenix, AZ, USA

### **EXECUTIVE COMMITTEE**

President: Jean-Luc Gaudiot

President-Elect: Hironori Kasahara; Past President: Roger U. Fujii; Secretary: Forrest Shull; First VP, Treasurer: David Lomet; Second VP, Publications: Gregory T. Byrd; VP, Member & Geographic Activities: Cecilia Metra; VP, Professional & Educational Activities: Andy T. Chen; VP, Standards Activities: Jon Rosdahl; VP, Technical & Conference Activities: Hausi A. Müller; 2017–2018 IEEE Director & Delegate Division VIII: Dejan S. Milojičić; 2016–2017 IEEE Director & Delegate Division V: Harold Javid; 2017 IEEE Director-Elect & Delegate Division V-Elect: John W. Walz

### BOARD OF GOVERNORS

Term Expiring 2017: Alfredo Benso, Sy-Yen Kuo, Ming C. Lin, Fabrizio Lombardi, Hausi A. Müller, Dimitrios Serpanos, Forrest J. Shull

Term Expiring 2018: Ann DeMarle, Fred Douglis, Vladimir Getov, Bruce M. McMillin, Cecilia Metra, Kunio Uchiyama, Stefano Zanero

**Term Expiring 2019:** Saurabh Bagchi, Leila De Floriani, David S. Ebert, Jill I. Gostin, William Gropp, Sumi Helal, Avi Mendelson

### EXECUTIVE STAFF

Executive Director: Angela R. Burgess; Director, Governance & Associate Executive Director: Anne Marie Kelly; Director, Finance & Accounting: Sunny Hwang; Director, Information Technology & Services: Sumit Kacker; Director, Membership Development: Eric Berkowitz; Director, Products & Services: Evan M. Butterfield; Director, Sales & Marketing: Chris Jensen

### COMPUTER SOCIETY OFFICES

Washington, D.C.: 2001 L St., Ste. 700, Washington, D.C. 20036-4928

Phone: +1 202 371 0101 • Fax: +1 202 728 9614 • Email: hq.ofc@computer.org

Los Alamitos: 10662 Los Vaqueros Circle, Los Alamitos, CA 90720

Phone: +1 714 821 8380 • Email: help@computer.org

Membership & Publication Orders

Phone: +1 800 272 6657 • Fax: +1 714 821 4641 • Email: help@computer.org

Asia/Pacific: Watanabe Building, 1-4-2 Minami-Aoyama, Minato-ku, Tokyo 1070062, Japan • Phone: +81 3 3408 3118 • Fax: +81 3 3408 3553 • Email: tokyo.ofc@

computer.org

### IEEE BOARD OF DIRECTORS

President & CEO: Karen Bartleson; President-Elect: James Jefferies; Past President: Barry L. Shoop; Secretary: William Walsh; Treasurer: John W. Walz; Director & President, IEEE-USA: Karen Pedersen; Director & President, Standards Association: Forrest Don Wright; Director & VP, Educational Activities: S.K. Ramesh; Director & VP, Membership and Geographic Activities: Mary Ellen Randall; Director & VP, Publication Services and Products: Samir El-Ghazaly; Director & VP, Technical Activities: Marina Ruggieri; Director & Delegate Division V: Harold Javid; Director & Delegate Division VIII: Dejan S. Milojičić

revised 31 May 2017

### If You Build It, Will They Come?

**Srilatha Manne** *Cavium*

**Bryan Chin** *University of California, San Diego*

**Steven K. Reinhardt** *Microsoft*

All hardware companies face a conundrum. Should they continue the evolutionary trend of their current products, or build riskier products that have the potential for greater reward but carry a higher probability of failure? The safe course, and one that many customers ask for, is the former. However, as Clayton Christensen points out in The Innovator's Dilemma, "most companies with a practiced discipline of listening to their best customers and identifying new products that promise greater profitability and growth are rarely able to build a case for investing in disruptive technologies until it is too late."1

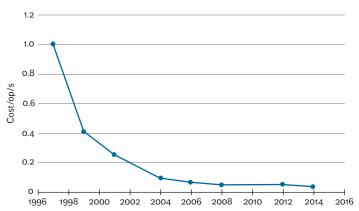

Computer hardware companies expend enormous resources to successfully improve their products in an evolutionary fashion. Single-threaded processor performance has been improving at a rate of 15 to 20 percent per year by utilizing both process technology and architectural improvements.<sup>2</sup> These improvements, however, are increasingly difficult to achieve. Using data from Moein Khazraee and colleagues,<sup>3</sup> Figure 1 shows that a processor's cost per operation, as defined by a combination of fabrication, nonrecurring engineering (NRE), and packaging costs, has not significantly improved in the past decade. However, performance improvements are flattening out due to

power restrictions and the breakdown of Dennard scaling. For instance, Intel is no longer relying on the tick-tock model, which it rode to market dominance for the past decade, due to the declining benefits of process technology scaling.<sup>4</sup>

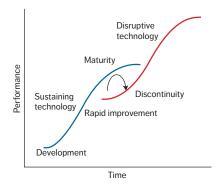

### Sustaining versus Disruptive Technology

Christensen describes the evolutionary process of improvements using the *sustaining technology S-curve* (see Figure 2). For every successful technology, the performance metric is initially flat during development, rapidly improves for a period of time, and flattens out again when the product and/or technology reaches maturity. Sustaining technologies are dominating the processor industry, and these technologies are reaching a plateau.

Sometimes a disruptive technology with a new S-curve will enter the landscape, as shown in Figure 2. Disruptive technologies do not go head to head with mainstream technologies, but they do have features that a few fringe markets value. Typically, disruptive technologies initially underperform, but then rapidly match and exceed the previous technology. Successful companies not only ride their sustaining S-curves but generate new,

disruptive curves to improve performance as the current technology curve flattens out. Microprocessors were once a disruptive technology, and the computing landscape over the past few decades is littered with disruptive technologies, from minicomputers to PCs to smartphones to cloud computing. In all these cases, the disruptive technology yielded worse performance in the near-term when using the same cost function as mainstream technology. However, as Christensen maintains, disruptive technologies eventually redefine how performance is measured.

Recent examples of disruptive technologies in processor architecture include GPUs and Arm servers. GPUs were originally designed for 3D graphics processing, but have made significant inroads first in high-performance computing (HPC) and more recently in machine learning. For applications that are similar to those found in SPECint, GPUs underperform general-purpose processors. However, for targeted HPC applications and machine learning, GPUs are overwhelmingly superior.

Arm processors originally targeted power-constrained embedded domains, but have more recently entered the server market with product offerings from companies such as Cavium and Qualcomm that address multicore throughput computing.<sup>5,6</sup> A new S-curve could develop for these specialized throughput-based server products—enabled by highly parallelizable shared-memory applications—just as it did with HPC and machine learning in the GPU market.

It took the GPU market nearly two decades to make headway outside of graphics applications, and the Arm server market has resulted in several failures. Christensen notes that this commonplace in disruptive markets is where "[it] is simply impossible to predict with any useful degree of precision how disruptive products will be used or how large their markets will be." So, how does one innovate in a rapidly changing technology landscape where the underlying cost function is in flux? How does a company keep up with the necessary and expensive evolutionary changes, yet also prepare for and justify expending valuable resources investigating disruptive technologies that are inevitable?

### The Case for Agility

Companies and their mainstream customers alike are notoriously bad at predicting what disruptive products will take root in the marketplace. There are many instances of high-profile developments that flopped. For example, it is unlikely you are reading this article on your Apple Newton while listening to music on your Microsoft Zune. Conversely, some disruptive technologies have found success in surprising places such as GPUs. Innovation in a rapidly changing landscape is difficult and prone to failure. Therefore, we posit that architects, rather than trying to predict the future, should pursue agility in order to accelerate innovation while minimizing costs. Hardware companies, architects, and the underlying design methodologies and infrastructure must be nimble enough to deal with disruptive technologies that come from within and outside the

**Figure 1.** Processor computation cost as a function of time. Cost is defined as a combination of fabrication, nonrecurring engineering (NRE), and packaging costs.<sup>3</sup>

current technology landscape. The rest of the article presents some ideas on how this may be accomplished.

### **Agile Architecture**

In his book The Lean Startup: How Today's Entrepreneurs Use Continuous Innovation to Create Radically Successful Business,7 Eric Ries writes about software companies that use agile software development strategies. The premise is to deliver prototypes as quickly as possible, even if haphazardly put together, to get early customer feedback. The goal is to use customer feedback to drive product features and direction through a process of continuous development. If you consider how frequently the apps on your phone are updated, or the look and feel of social networking sites evolve, you have seen agile software practices in action.

Facebook, for example, uses agile coding practices. As Kent Beck explains, one of the basic practices at Facebook is reversibility. If a decision is reversible, it does not require the rigorous testing that irreversible decisions require. Code is also released incrementally to a small subset of users, which enables changes to be rolled back with minimal disruption if a problem is found. The challenge for the hardware industry is how to adapt a similar agile methodology without incurring large overheads. We address this

**Figure 2.** The sustaining technology and disruptive technology S-curves.

challenge in both traditional processor hardware methodologies and innovative methodologies utilized by large computing companies.

### **Processor Agility**

Prior to the ASIC revolution of the past few decades, hardware prototypes were a common means of achieving the rapid development and early feedback cycle. Old technologies such as wire-wrap, breadboards, programmable logic devices (PLDs), and low-cost printed circuit boards (PCBs) enabled hardware companies to quickly build and iterate on products. This methodology is no longer feasible given the complexity and cost of processor development both in terms of engineering time and fabrication costs.<sup>3</sup>

Automated design methodology and reuse. Companies today rely on improved design methodologies and reusability to reduce design time and cost. Design methodologies have made great strides in the past two decades, resulting in shorter design cycle times and an expanded product portfolio using the same fundamental components. Most processors, even those designed for high performance, are mostly or completely synthesized. The Arm roadmap has synthesized cores operating at 3 GHz, and AMD, Intel, and IBM extensively use automated tools throughout their design. 10-12 In addition, companies utilize a modular design methodology such that multiple products can be developed using the same basic components.

Both Intel and AMD use their respective base core designs and innovative packaging technologies to build products ranging from low-power mobile parts to multicore server products.<sup>13</sup> Similarly, silicon companies such as Cavium and Nvidia have been able to create a family of devices with varying price/performance points from the same basic design by utilizing flexible chip layouts that let designers vary the number of computational units and/or the amount of on-die memory. Intel has taken this one step further by collaborating with Facebook to develop a specialized version of Broadwell (referred to as Broadwell-D) to meet the specific needs of Facebook. 14

The technologies mentioned so far reduce design cycle time, but there is still significant overhead associated with bringing a chip to production. Post-silicon functional and performance debug is a formidable challenge for modern processors that may encompass multiple sockets, heterogeneous and/or multithreaded cores, many cores combined with multiple levels of memory hierarchy, complex memory coherence and consistency protocols, and extensive power and performance management via on-chip controllers. In addition,

modern processors may operate under complex software stacks containing one or more nested virtual environments. For these reasons, even with mostly synthesized methodologies and reuse of existing components, the transition from first silicon to full production part can take up to a year or more. <sup>15</sup>

Functional verification and bug mitigation. Post-production bugs are commonplace, and fixing bugs in shipped products often involves errata, metal and full-layer spins, and/or replacing existing silicon. Infamous examples of such bugs are the Pentium FDIV bug, 16 the Haswell/Broadwell transactional memory bug,<sup>17</sup> and the AMD TLB bug.<sup>18</sup> These bugs cost the respective companies millions of dollars in lost revenue, and in AMD's case, contributed to its loss of momentum in the server market. All processors have a large list of errata. The table of known errata in Haswell, for instance, covers six pages.<sup>19</sup>

To meet market needs and address the complexity and cost of post-silicon debug, architects must focus on hardware and software solutions for exposing, analyzing, and mitigating functional and performance bugs. Processor vendors must provide tools that rapidly expose and identify bugs and have systems in place for mitigating these bugs without the need for extensive silicon changes. Efforts such as Arm's hardware debug architecture attempt to standardize the infrastructure so that common tools can be made available to the Arm hardware development ecosystem.<sup>20</sup>

Both software and hardware solutions should be explored for mitigating hardware bugs in the field. On the hardware front, microcode fixes on traditional CISC processors come to mind, as does the PAL (Privileged Architecture Library) code feature of DEC's Alpha processors. A similar technology that might help processor vendors mitigate bugs is virtual machine environments.

Much software these days is compiled to an abstract machine. Two examples of such abstraction layers, one current and one historical, are Oracle's Java Virtual Machine (JVM)<sup>21</sup> and IBM's AS/400 Series.<sup>22</sup> If an entire processor is designed to execute only a JVM, then the JVM itself provides the instruction set architecture (ISA) of the machine, and the underlying physical machine may have bugs or features that are invisible to the JVM. The JVM addresses ISA-related bugs. Similarly, more fully specified virtual machine environments, such as VMware's vSphere and Microsoft's Hyper-V, virtualize system aspects of the machine, such as memory management and I/O. Machines such as IBM's AS/400 managed to maintain a stable abstract architecture through multiple generations of hardware. By expecting and architecting for bug discovery, analysis, and mitigation, processor vendors can reduce the number of bugs that reach production silicon, and respond to issues in post-production parts quickly and effectively. This shortens the designer-customer feedback loop and leads to a faster development cycle and improved successor products.

verification Performance and optimization. Another critical facet of bringing a processor to production is performance tuning. Processors are designed with dozens of control bits (also referred to as chicken bits) to manage system performance. Some chicken bits are exposed to the user (for example, disabling prefetching or simultaneous multithreading mode, or restricting power management), and others are known only by the manufacturer. Regardless, how these bits are set and tuned can have a significant impact on performance. Unfortunately, there are hundreds of these interdependent knobs, and tuning them by hand is impractical. However, self-tuning systems, either integrated into the operating system or as separate tools,<sup>23</sup>

that can dynamically adjust these bits according to application needs may be an innovative mechanism for achieving optimal performance. Best of all, these tuners can be deployed on-site, which means they do not gate product release to customers. Finally, the same techniques for fixing bugs via low-level software or implementing a virtual machine can also be used to adapt silicon to new applications. Hardware designers can enable and deploy new instructions and features through the same mechanisms used to patch around bugs. New versions of a JVM implementation, for example, may exploit optimizations that are relevant to new application areas.

### **Computational Agility**

So far, we have addressed agility at the processor level. However, with the advent of warehouse-scale systems driven by cloud computing, the processor becomes one piece of a larger computational problem. New companies entering the computing arena include numerous startups and large, established companies from outside the traditional chip design industry, such as Google, Microsoft, and Amazon. Few if any of these companies are choosing to go head-to-head in the general-purpose processor market with traditional designs such as Intel and AMD. Rather, they are achieving agility via specialized devices targeting narrower but highly relevant domains.

The need for specialization. The end of Dennard scaling and the slowdown and imminent demise of Moore's law drive the need for specialization, just as they demand agility in processor design. During the steep part of the S-curve for general-purpose processors, specialized architectures were quickly outpaced by these cheaper commodity devices. The slowing rate of improvement in general-purpose designs both creates opportunity for specialized architectures and drives demand, as

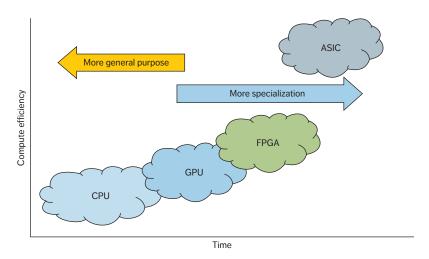

Figure 3. Specialization trend over time.

customers can no longer rely on the commodity market to satisfy their computing needs.

A prerequisite for specialization is identifying an application or application domain narrow enough to benefit from specialization but large enough to justify a specialized device. Focusing on smaller and smaller domains (down to specific applications) increases the amount of potential performance uplift through specialization, while decreasing the potential market. To be successful, the total value created through specialization (roughly speaking, the value per device times the number of devices) must exceed the cost of developing the specialized device. By developing agile methodologies that reduce engineering costs, we can enable specialization for smaller domains and allow specialized devices to emerge sooner in growing markets.

Figure 3 shows the specialization trend over time, starting with CPUs and ending with custom ASICs. Cryptocurrency mining followed this trend,<sup>24</sup> and deep learning, one of the most prominent new markets attracting specialized architectures, is following suit. GPUs offer better performance than CPUs for certain tasks, such as training for AI, whereas state-of-the

art field-programmable gate arrays (FPGAs) can outperform standard GPUs for certain computations such as low-precision arithmetic.<sup>25</sup> Finally, custom ASIC accelerators provide the highest performance efficiency.

Multiple startups such as Graphcore, Wave Computing, Nervana (now part of Intel), and Groq are developing or have developed customized deep learning accelerators that occupy the upper right corner of Figure 3. However, one of the earliest and most publicized deep learning accelerators is not from a startup but from an established company without a history of chip design. The Google Tensor Processing Unit (TPU) was developed in a short 15 months.<sup>26</sup> To achieve a rapid production cycle, Google used an older and more stable process technology (28 nm) and existing communication interfaces. The first-generation TPU was for internal use and had computational and memory bandwidth limitations. However, the TPU is now on its second iteration, and it not only supports higher computational capability and memory bandwidth, but will reportedly be made accessible to third parties.<sup>27</sup>

Even in an agile environment, the delay from the initial ASIC concept

to fully deployed device is measured in years. Once deployed, ASICs must continue to provide value for multiple additional years before replacement. Thus, an ASIC must accelerate a function that, from the point of conception, will still be valuable four to five years in the future. While some functions, such as compression and encryption algorithms, tend to be stable over these time frames, those in rapidly evolving fields such as deep learning may develop new and different requirements in the interval from design start to deployment. Stable, high-volume accelerators can easily justify an ASIC's higher nonrecurring engineering cost. Because an ASIC design needs larger markets and longer lifetimes, an ASIC accelerator typically includes as much flexibility as designers can afford in the form of configuration parameters, options, and software programmability.

To achieve a more agile acceleration framework, Microsoft took an unusual approach to specialization by focusing on FPGAs rather than ASICs for datacenter acceleration.<sup>28</sup> For a given accelerator design, an FPGA implementation could be several times slower and less energy efficient than an ASIC implementation. However, by using hardware devices that can be reprogrammed after deployment, Microsoft gains agility at the expense of computational efficiency. FPGA-based accelerators not only are tolerant to the changing requirements of a given application, but can be completely retargeted as new applications emerge or demand shifts. An FPGA accelerator design can afford to be less configurable and more customized to specific situations, as the design itself can be incrementally modified after initial deployment to address new circumstances. In this fashion, the FPGA's agility as a platform can be used to recover a portion of the efficiency that it sacrifices to an equivalent ASICbased design.

FPGAs can also close the gap with ASICs by incorporating larger and more complex hard logic blocks on chip. Current FPGAs include multiply-accumulate units and even full microprocessor cores as hard logic. Researchers have also proposed devices that are mostly hard logic, but with configurable interconnect, referred to as coarse-grained reconfigurable accelerators (CGRAs).<sup>29</sup> The line between FPGAs and ASICs is further blurred by integrated multichip packages that incorporate both an FPGA and ASIC die. 30 The ability for customers to specify which ASICs are included in the package provides yet another dimension of flexibility.

### The computational marketplace.

Amazon has also developed hardware for internal consumption from custom routers to chipsets used in its servers.<sup>31</sup> This enables Amazon to optimize the hardware for its specific needs with full control of both the hardware and software stack. Amazon also provides hardware agility to its customers by offering platforms for custom programmable hardware as part of the AWS services plan.<sup>32</sup> The goal is to encourage companies to develop accelerators using Amazon's FPGA framework for internal use and/or sell the resulting computational capability to end customers on the AWS Marketplace. Amazon's EC F1 instances with FPGAs offer two significant benefits for custom solution developers. First, Amazon provides the FPGA hardware, tools, and infrastructure, significantly lowering the cost and convenience threshold for developing customized hardware. Second, Amazon provides a deployment model (via AWS) and a ready marketplace of potential customers for the final product. No longer are hardware developers restricted to products with a large Tier One customer base. They can rapidly develop and deploy niche hardware and test its viability in the AWS computational marketplace with many small

customers across the country and the world. The computational marketplace scenario comes closest to achieving the rapid deployment model highlighted in *The Lean Startup*.<sup>7</sup> Finally, if any of these customized solutions become pervasive, they can eventually be reimplemented as an ASIC, as noted by Khazraee,<sup>3</sup> or integrated into a general-purpose processor architecture.

Standardized ecosystem. A successful computational marketplace requires standardized interfaces for interacting with accelerators. On the hardware side, current solutions from Amazon, Microsoft, Google, and others rely on PCIe for accelerator integration. PCIe has been the de facto standard for peripherals for many years, and a part of its success can be attributed to having an open standard. However, for processor designers wanting to create specialized accelerators, PCIe may not offer the tightly coupled memory system integration desired or required by the application. Proprietary coherent processor interconnects such as Intel's QPI and AMD's Infinity Fabric offer the memory system integration that a specialized accelerator might require, while Nvidia's NVLink is a proprietary interconnect for GPUs. Nonproprietary standards from different consortia such as OpenCAPI (www.opencapi .org), Gen-Z (www.genzconsortium .org), and CCIX (www.ccixconsortium .com) might also supplement PCIe as these standards evolve. What is clear, from the PCIe example, is that the new standard should be easily licensable and controlled by an open standards organization to enable a level playing

While we have thus far emphasized agility in hardware development and deployment, software agility is also a critical requirement. An environment in which hardware capabilities change and evolve rapidly is impossible to use unless low-level software can adapt equally rapidly, while providing stable

APIs to higher-level services so that the bulk of the code base can remain independent of the underlying implementation's details. Software stacks can provide additional agility when they help to automate the mapping of applications to accelerators, and enable hardware bug workarounds to cope with issues that may slip through an accelerated development and testing schedule.

rocessor architecture has changed significantly over the past few decades with the advent of multicore designs, design for low power, heterogeneous systems, and many-core processors that can run a hundred or more threads. With cloud computing and the emerging customizable marketplace of products, we are once again witnessing a sea change in the way computing takes place.

In this article, we have made a case for agility because we cannot predict the future with any level of accuracy. We need agility not only for rapid evolution of conventional architecture, but also for lowering the barrier for specialized architectures. As Bill Gates once noted, "We always overestimate the change that will occur in the next two years and underestimate the change that will occur in the next ten. Don't let yourself be lulled into inaction."33 As architects, we must develop the infrastructure and mindset that enable us to be agile and take risks in order to evolve with a rapidly changing environment and create the next disruptive technology. [ii]

### References

- C.M. Christensen, The Innovator's Dilemma: When New Technologies Cause Great Firms to Fail, Harvard Business School Press, 1997.

- 2. "A Look Back at Single-Threaded CPU Performance," blog, 8 Feb. 2012; http://preshing . c o m / 2 0 1 2 0 2 0 8 / a l o o k

- -back-at-single-threaded-cpu -performance.

- 3. M. Khazraee et al., "Moonwalk: NRE Optimization in ASIC Clouds," Proc. 22nd Int'l Conf. Architectural Support for Programming Languages and Operating Systems, 2017, pp. 511–526.

- 4. J. Hruska, "Intel Formally Kills its Tick-Tock Approach to Processor Development," blog, 23 Mar. 2016; www.extremetech.com/extreme/225353-intel-formally-kills-its-tick-tock-approach-to-processor-development.

- 5. T.P. Morgan, "Qualcomm Fires ARM Server Salvo, Broadcom Silences Guns," 7 Dec. 2016; www .nextplatform.com/2016/12/07/qualcomm-fires-arm-server-salvo-broadcom-silences-guns.

- R. Brueckner, "Cavium ThunderX2 Processors Power New Baymax HyperScale Server Platforms," blog, 29 May 2017; http://insidehpc.com/2017/05/cavium-thunderx2-processors-power-new-baymax-hyperscale-server-platforms.

- 7. E. Ries, The Lean Startup: How Today's Entrepreneurs Use Continuous Innovation to Create Radically Successful Business, Crown Publishing Group, 2011.

- 8. C. Murphy, "Facebook Guru and Agile Pioneer Kent Beck Reveals the Mind of the Modern Programmer," Forbes, 9 Jan. 2017; www.forbes.com/sites/oracle/2017/01/09/facebook-guru-and-agile-pioneer-kent-beck-reveals-the-mind-of-the-modern-programmer.

- 9. J. Bird, "This Is How Facebook Develops and Deploys Software. Should You Care?" blog, 4 Sept. 2013; http://dzone.com/articles/how-facebook-develops-and.

- M. Humrick, "Exploring DynamIQ and ARM's New CPUs: Cortex-A75, Cortex-A55," blog,

- 29 May 2017; www.anandtech .com/show/11441/dynamiq-and -arms-new-cpus-cortex-a75 -a55.

- 11. P. Gelsinger et al., "Such a CAD! Coping with the Complexity of Microprocessor Design at Intel," *IEEE Solid-State Circuits*, vol. 2, no. 3, 2010, pp. 32–43.

- 12. M. Ziegler, R. Puri, and B. Philhower, "POWER8 Design Methodology Innovations for Improving Productivity and Reducing Power," *Proc. IEEE Custom Integrated Circuits Conf.*, 2014, pp. 1–9.

- 13. A. Patrizio, "Intel Shakes Up Its Chip Design Process," blog, 23 May 2014; www.itworld .com/article/2699164/hardware /intel-shakes-up-its-chip-design -process.html.

- 14. V. Rao and E. Smith, "Facebook's New Front-End Server Design Delivers on Performance without Sucking Up Power," blog, 9 Mar. 2016; http://code.facebook.com/posts/1711485769063510/facebook-s-new-front-end-server-design-delivers-on-performance-without-sucking-up-power.

- 15. M. Abramovici and P. Bradley, "A New Approach to In-System Silicon Validation and Debug," *EE Times*, 16 Sept. 2007; www.eetimes.com/document .asp?doc\_id=1276099.

- "Pentium FDIV Bug," blog; www .cs.earlham.edu/~dusko/cs63 /fdiv.html.

- 17. S. Wasson, "Errata Prompts Intel to Disable TSX in Haswell, Early Broadwell CPUs," blog, 12 Aug. 2014; http://techreport.com/news/26911/errata-prompts-intel-to-disable-tsx-in-haswell-early-broadwell-cpus.

- 18. K. Kubicki, "Understanding AMD's

'TLB' Processor Bug," blog, 5

Dec. 2007; www.dailytech.com

/Understanding++AMDs+TLB

+Processor+Bug/article9915

.htm.

- 19. Desktop 4th Generation Intel Core Processor Family, Desktop Intel Pentium Processor Family, and Desktop Intel Celeron Processor Family, report 328899-037US, Mar. 2017.

- 20. "Debug Architecture Overview," ARM, 2017; http://developer.arm .com/products/architecture/debug -architecture

- 21. T. Lindholm et al., *The Java Virtual Machine Specification: Java SE 7 Edition*, 28 Feb. 2013.

- 22. F.G. Soltis, *Inside the AS/400: Featuring the AS/400e Series*, 2nd ed., 29th Street Press, 1997.

- 23. T. Morad, *The Era of Self-Tuning Servers*, 7 Feb. 2017; www .hpcadvisorycouncil.com/events /2017/stanford-workshop/pdf /Morad\_TheEraOfSelfTuning Servers.pdf.

- 24. P. Jama, "The Future of Machine Learning Hardware," blog, 10 Sept. 2016; http://hackernoon.com/the-future-of-machine-learning-hardware-c872a0448be8.

- 25. L. Barney, "Can FPGAs Beat GPUs in Accelerating Next-Generation Deep Learning?" blog, 21 Mar. 2017; www.nextplatform.com/2017/03/21/can-fpgas-beat-gpus-accelerating-next-generation-deep-learning.

- 26. K. Sato, C. Young, and D. Patterson, "An In-Depth Look at Google's First Tensor Processing

- Unit (TPU)," blog, 12 May 2017; http://cloud.google.com/blog/big-data/2017/05/an-in-depth-look-at-googles-first-tensor-processing-unit-tpu.

- 27. P. Teich, "Under the Hood of Google's TPU2 Machine Learning Clusters," blog, 22 May 2017; www .nextplatform.com/2017/05/22 /hood-googles-tpu2-machine -learning-clusters.

- 28. A. Putnam et al., "A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services," blog, 1 June 2014; www.microsoft.com/en-us/research/publication/a-reconfigurable-fabric-for-accelerating-large-scale-datacenter-services.

- 29. M. Gao and C. Kozyrakis, "HRL: Efficient and Flexible Reconfigurable Logic for Near-Data Processing," *Proc. IEEE Int'l Symp. High Performance Computer Architecture*, 2016, doi: 10.1109/HPCA.2016.7446059.

- 30. M. Deo, Enabling Next-Generation Platforms Using Intel's 3D System-in-Package Technology, white paper WP-01251-1.5, Intel, Aug. 2017.

- 31. D. Richman, "Amazon Web Services' Secret Weapon: Its Custom-Made Hardware and Network," blog, 19 Jan. 2017; www.geekwire.com/2017/amazon-web-services

- -secret-weapon-custom-made -hardware-network.

- 32. "Amazon EC2 F1 Instances, Customizable FPGAs for Hardware Acceleration Are Now Generally Available," blog, 19 Apr. 2017; http://aws.amazon.com/about-aws/whats-new/2017/04/amazon-ec2-f1-instances-customizable-fpgas-for-hardware-acceleration-are-now-generally-available.

- 33. B. Gates, *The Road Ahead*, Viking Penguin, 1996.

**Srilatha Manne** is a principal hardware architect at Cavium. Contact her at bobbiemanne12@gmail.com.

Bryan Chin is a lecturer in the Computer Science and Engineering Department at the University of California, San Diego. Contact him at b5chin @ucsd.edu.

**Steven K. Reinhardt** is a partner hardware engineering manager at Microsoft. Contact him at stever@microsoft.com.

## Blurring the Lines between Memory and Computation

**Reetuparna Das** University of Michigan

### Computer designers have traditionally

separated the roles of storage and computation. Memories stored data. Processors computed them. Is this distinction necessary? A human brain does not separate the two so distinctly, so why should a computer? Before addressing this question, let us start with the well-known memory wall problem.<sup>1</sup>

What is the memory wall in today's context? The memory wall originally referred to the problem of growing disparity in speed between fast processors and slow memories. Since 2005 or so, as processor speed flatlined, memory latency has remained about the same. But as the number of processor cores per chip kept increasing, memory bandwidth and memory energy became more dominant issues. A significant fraction of energy is spent today in moving data back and forth between memory and computing units, a problem that is exacerbated in modern data-intensive systems.

How do we overcome the memory wall in today's computing world that is increasingly dominated by data-intensive applications? For well over two decades, architects have tried a variety of strategies to overcome the memory wall. Most of them have centered on exploiting locality. Here is an alternative: what if we could move computation closer to memory—so

much that the line that divides computation and memory starts to blur?

### The First Wave

Researchers discussed processing in memory (PIM) in the 1990s<sup>2–6</sup> (initial suggestions date back to as early as the 1970s<sup>7</sup>) as an alternative solution to scale the memory wall. The key idea was to physically bring the computation and memory units closer together by placing computation units inside the main memory (DRAM). But this idea did not quite take off back then, due to the high cost of integrating computational units within a DRAM die. Another factor may have been the fact that cheaper optimizations were still possible, thanks to Moore's law and Dennard scaling.

The advent of commercially feasible 3D chip stacking technology, such as Micron's Hybrid Memory Cube (HMC),<sup>8</sup> has renewed our interest in PIM. HMC stacks layers of DRAM memory on top of a logic layer. Computational units in the logic layer can communicate with memory through high-bandwidth through-silicon vias. Thanks to 3D integration technology, we can now take computational and DRAM dies implemented in different process technologies and stack them on top of each other.

The additional dimension in 3D PIM allows an order of magnitude

more physical connections between the computational and memory units, and thereby provides massive memory bandwidth to the computational units. 9-15 The available memory bandwidth is so high in these systems that a general-purpose multicore processor with tens of cores is a poor candidate to take advantage of 3D PIM. The bandwidth of cheaper conventional DRAM is mostly adequate for these general-purpose processors. Better candidates are customized computational units that can truly take advantage of the abundant memory bandwidth in 3D PIM data-parallel accelerators, such as a GPU, or even better, customized accelerators such as Google's Tensor Processing Unit. 16

Although 3D PIM is a clear winner in terms of memory bandwidth compared to conventional DRAM, its latency and energy advantages are perhaps exaggerated in literature. 3D PIM brings computation closer to DRAM memory. It has no effect on the energy spent accessing data within DRAM layers, DRAM refresh and leakage, and on-die interconnect in the logic layer, which together happen to be the dominant cost. To be clear, there is some memory latency and energy reduction as it eliminates communication over the off-chip memory channels by integrating computation in 3D PIM's logic

layer. However, this benefit is not likely to be a big win and paves a smaller step toward reducing the steep data-movement overheads. 17,18

### **The Second Wave**

Although PIM brings computational and memory units closer together, the functionality and design of memory units remains unchanged. An even more exciting technology is one that dissolves the line that distinguishes memory from computational units. Nearly three-fourths of silicon in processor and main memory dies is simply to store and access data. What if we could take this memory silicon and repurpose it to do computation? Let us refer to the resulting unit as *Compute Memory*.

Compute Memory repurposes the memory structures, the ones that are traditionally used only to store data, into active computational units for near-zero area cost. Compute Memory's biggest advantage is that its memory arrays morph into massive vector computing units (potentially, one or two orders of magnitude larger than a GPU's vector units), as data stored across hundreds of memory arrays could be operated on concurrently. Because we do not have to move data in and out of memory, the architecture naturally saves the energy spent in those activities, and memory bandwidth becomes a meaningless metric.

Micron's Automata Processor (AP)<sup>19,20</sup> is an example for Compute Memory. It transforms DRAM structures to a Nondeterministic Finite Automata (NFA) computational unit. NFA processing occurs in two phases: state match and state transition. AP cleverly repurposes the DRAM array decode logic to enable state matches. Each of the several hundreds of memory arrays can now perform state matches in parallel. The state-match logic is coupled with a custom interconnect to enable state transition. We can process as many as 1,053 regular expressions in Snort (a classic network-intrusion detection system) in one go using little more than DRAM hardware. AP can be an order of magnitude more efficient than GPUs and nearly two orders of magnitude more efficient than general-purpose multicore CPUs! Imagine the possibilities if we can sequence a genome within minutes using cheap DRAM hardware.

AP repurposed just the decode logic in DRAMs. Could we do better? In our recent work on Compute Caches, 21,22 we showed that it is possible to repurpose SRAM array bit-lines and sense-amplifiers to perform in-place analog bit-line computation on the data stored in SRAM. A cache is typically organized as a set of sub-arrays; as many as thousands of sub-arrays, depending on the cache level. 23–25 These sub-arrays can all compute concurrently on several hundred thousands of data elements stored in them with little extensions to the existing cache structures, while incurring an overall area overhead of 4 percent. Thus, caches can effectively function as large vector computational units, whose operand sizes are orders of magnitude larger than conventional SIMD units. Of course, it also eliminates the energy spent in moving data in and out of caches. While our initial work supports few useful operations (logical, search, and copy), we believe that it is just a matter of time before we are able to support more complex operations (including comparisons, addition, multiplication, sorting).

Supporting Compute Caches' style-in-place, analog bit-line computing in DRAMs is more challenging. The problem is that DRAM reads are destructive—one reason why DRAMs need periodic refresh. Although in-place DRAM computing may not be possible, an interesting solution is to copy the data to a temporary row in the DRAM8 and then do bit-line computing. This approach will incur extra copies, but retains the massive parallelism benefits.

Unlike DRAMs, bit-line computing may work well in a diverse set

of nonvolatile memory technologies (RRAMs, STT-MRAMs, and Flash). Researchers have already found success in repurposing structures in emerging NVMs to build efficient ternary content-addressable memory (TCAM)<sup>26</sup> and neural networks.<sup>27–29</sup>

Computational memories can be massively data parallel—potentially, an order of magnitude more performance and energy efficient than modern data-parallel accelerators such as GPUs. Such dramatic improvements could have a transformative effect on applications ranging from genome sequencing to deep neural networks. However, capabilities of computational memories may not be as general purpose as GPUs are today, and may impose additional constraints in terms of where data is stored. Application developers may have to rework their algorithms to fully take advantage of Compute Memory. Modern dataparallel domain-specific language frameworks such as CUDA and Tensorflow can be adapted to help these developers. It may also require runtime and system software support to meet computational memory constraints such as data placement.

As the general-purpose core's effi-ciency flatlined over the past decade, both industry and academia have wholeheartedly embraced customization of computational units. It is high time for us to think about customizing memory units as well. While there are many ways that one could think of customizing memory, turning it into powerful accelerators is one of the more exciting avenues to pursue. Until recently, we have viewed computing and memory units as two separate entities. Even within a processor, caches and computational logic have operated as two separate entities that served different roles. The time has come to dissolve the line that separates them. III

### References

- 1. W.A. Wulf and S.A. McKee, "Hitting the Memory Wall: Implications of the Obvious," *SIGARCH Computer Architecture News*, vol. 23, no. 1, 1995, pp. 20–24.

- 2. M. Gokhale, B. Holmes, and K. Iobst, "Processing in Memory: The Terasys Massively Parallel PIM Array," *Computer*, 1995, vol. 28, no. 4, 1995, pp. 23–31.

- Y. Kang et al., "FlexRAM: Toward an Advanced Intelligent Memory System," Proc. Int'l Conf. Computer Design, 1999, pp. 192–201.

- P. Kogge, "Execube: A New Architecture for Scaleable MPPs," Proc. Int'l Conf. Parallel Processing, vol. 1, 1994, pp, 77–84.

- M. Oskin, F. Chong, and T. Sherwood, "Active Pages: A Computation Model for Intelligent Memory," Proc. 25th Ann. Int'l Symp. Computer Architecture, 1998, pp. 192–203.

- 6. D. Patterson et al., "A Case for Intelligent RAM," *IEEE Micro*, vol. 17, no. 2, 1997, pp. 34–44.

- 7. H.S. Stone, "A Logic-in-Memory Computer," *IEEE Trans. Computers*, vol. C-19, no. 1, 1970, pp. 73–78.

- 8. *Hybrid Memory Cube Specification*, 2014; http://hybridmemorycube.org.

- J. Ahn et al., "PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture," Proc. 42nd Ann. Int'l Symp. Computer Architecture, 2015, pp. 336–348.

- A. Farmahini-Farahani et al., "NDA: Near-Dram Acceleration Architecture Leveraging Commodity DRAM Devices and Standard Memory Modules," Proc. IEEE 21st Int'l Symp. High Performance Computer Architecture, 2015, pp. 283–295.

- D. Kim et al., "Neurocube: A Programmable Digital Neuromorphic Architecture with High-Density 3D Memory," Proc. 43rd Int'l

- *Symp. Computer Architecture*, 2016, pp. 380–392.

- 12. S. Pugsley et al., "NDC: Analyzing the Impact of 3D-Stacked Memory+Logic Devices on MapReduce Workloads," *Proc. IEEE Int'l Symp. Performance Analysis of Systems and Software*, 2014, pp. 190–200.

- 13. V. Seshadri et al., "RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization," *Proc. 46th Ann. IEEE/ACM Int'l Symp. Microarchitecture*, 2013, pp. 185–197.

- 14. D. Zhang et al., "Top-PIM: Throughput-Oriented Programmable Processing in Memory," Proc. 23rd Int'l Symp. High-Performance Parallel and Distributed Computing, 2014, pp. 85–98.

- Q. Zhu et al., "A 3D-Stacked Logic-in-Memory Accelerator for Application-Specific Data Intensive Computing," Proc. IEEE Int'l 3D Systems Integration Conf., 2013, doi:10.1109/3DIC.2013.6702348.

- 16. N.P. Jouppi et al., "In-Datacenter Performance Analysis of a Tensor Processing Unit," *Proc. 44th Ann. Int'l Symp. Computer Architecture*, 2017, pp. 1–12.

- 17. K. Bergman et al., ExaScale Computing Study: Technology Challenges in Achieving Exascale Systems, DARPA, 2008.

- 18. B. Dally, "Power, Programmability, and Granularity: The Challenges of ExaScale Computing," *Proc. IEEE Int'l Parallel Distributed Processing Symp.*, 2011, p. 878.

- 19. Micron Automata Processing; www.micronautomata.com.

- P. Dlugosch et al., "An Efficient and Scalable Semiconductor Architecture for Parallel Automata Processing," *IEEE Trans. Parallel* and Distributed Systems, vol. 25, no. 12, 2014, pp. 3088–3098.

- 21. S. Aga et al., "Compute Caches," *Proc. 23rd Int'l Symp. High Performance Computer Architecture*, 2017, pp. 481–492.

- S. Jeloka et al., "A Configurable TCAM/BCAM/SRAM using 28nm Push-Rule 6T Bit Cell," *Proc. IEEE Symp. VLSI Circuits*, 2015, pp. C272–C273.

- 23. W.J. Bowhill et al., "The Xeon R Processor E5-2600 v3: A 22 nm 18-Core Product Family," *J. Solid-State Circuits*, vol. 51, no. 1, 2016, pp. 92–104.

- 24. W. Chen et al., "A 22nm 2.5 MB Slice On-Die L3 Cache for the Next Generation Xeon R Processor," *Proc. IEEE Symp. VLSI Technology*, 2013, pp. C132–C133.

- 25. M. Huang et al., "An Energy Efficient 32-nm 20-MB Shared On-Die L3 Cache for Intel R Xeon R Processor E5 Family," *J. Solid-State Circuits*, vol. 48, no. 8, 2013, pp. 1954–1962.

- 26. Q. Guo et al., "Resistive Ternary Content Addressable Memory Systems for Data-Intensive Computing," *IEEE Micro*, vol. 35, no. 5, 2015, pp. 62–71.

- 27. M.N. Bojnordi and E. Ipek, "Memristive Boltzmann Machine: A Hardware Accelerator for Combinatorial Optimization and Deep Learning," *Proc. IEEE Int'l Symp. High Performance Computer Architecture*, 2016, pp. 1–13.

- 28. P. Chi et al., "Prime: A Novel Processing-in-Memory Architecture for Neural Network Computation in ReRAM-Based Main Memory," *Proc. 43rd Int'l Symp. Computer Architecture*, 2016, pp. 27–39.

- 29. A. Shafiee et al., "Isaac: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars," *Proc.* 43rd Int'l Symp. Computer Architecture, 2016, pp. 14–26.

Reetuparna Das is an assistant professor in the Electrical Engineering and Computer Science Department at the University of Michigan. Contact her at reetudas@umich.edu.

## Ultra-Low-Power Processors

### **David Brooks**

Harvard University

### John Sartori

University of Minnesota

ociety's increasing use of connected sensing and wearable computing has created robust demand for ultra-low-power (ULP) edge computing devices and associated system-on-chip (SoC) architectures. In fact, the ubiquity of ULP processing has already made such embedded devices the highest-volume processor part in production, with an even greater dominance expected in the near future. The Internet of Everything calls for an embedded processor in every object, necessitating billions or trillions of processors. At the same time, the explosion of data generated from these devices, in conjunction with the traditional model of using cloud-based services to process the data, will place tremendous demands on limited wireless spectrum and energy-hungry wireless networks. Smart, ULP edge devices are the only viable option that can meet these demands.

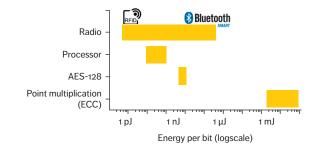

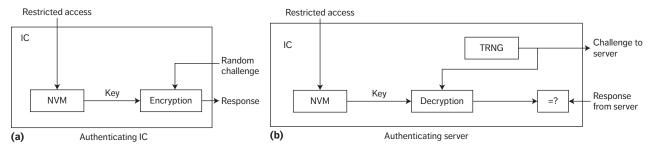

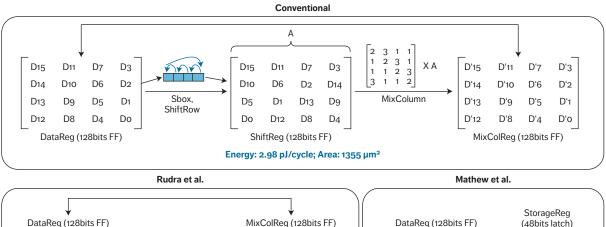

One big area of expansion for ULP processors is the Internet of Things (IoT). Most projections forecast the number of connected IoT devices to grow exponentially, easily reaching over 100 billion within the next decade. Even assuming a conservative ULP power budget of a few milliwatts per device, the total energy consumption of all these connected devices will be over 10 trillion kWh per year. That's more energy than over half of the countries in the world consume in a year. Given the sheer number of devices that will be connected (IoT devices will outnumber humans by more than an

order of magnitude), even trying to change or charge all their batteries will become an infeasible task, necessitating more research on energy harvesting to create energy-neutral devices that can fend for themselves by collecting their own energy. Likewise, more research will be needed on novel ways to reduce power dramaticallyby an order of magnitude or more, enabling ULP devices to be integrated in more places and in higher quantities. In conjunction with this research on ultra-low power and energy, the fact that all these devices will be connected to the Internet demands more research on energy-efficient security measures. In a world where IoT devices have access to all of our data—personal, health-critical, financial, and all the rest—the attack surface for potential information security leaks becomes larger than ever. With all this critical information entrusted to devices that can barely scrape together enough power to boot up, much less implement a host of security protocols, ensuring information security at ultra-low power and energy levels will be critical.

The articles in this special issue highlight some of the critical research and explore some of the potentially viable solutions that will help to advance the state of the art toward a more power- and energy-efficient future for ULP processing.

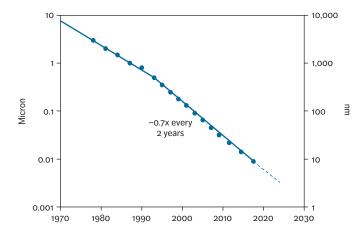

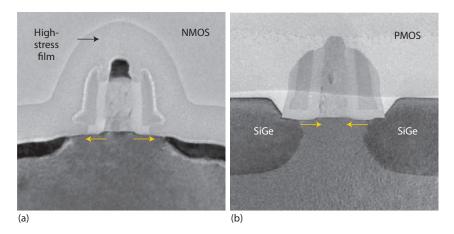

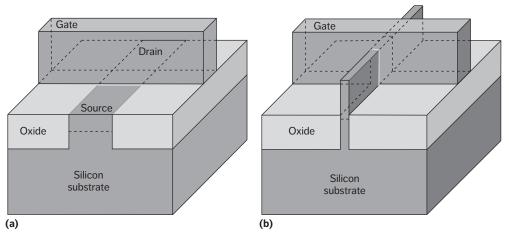

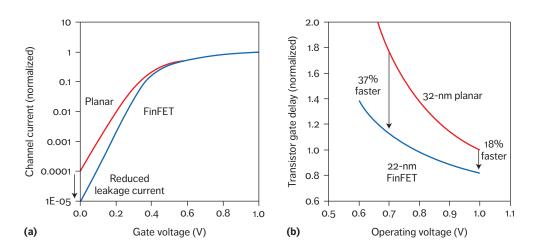

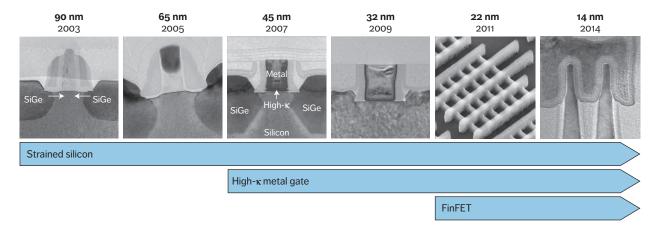

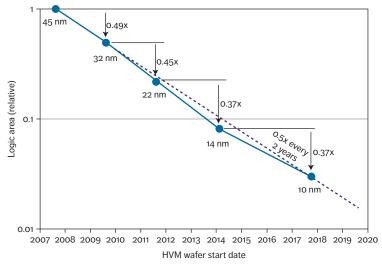

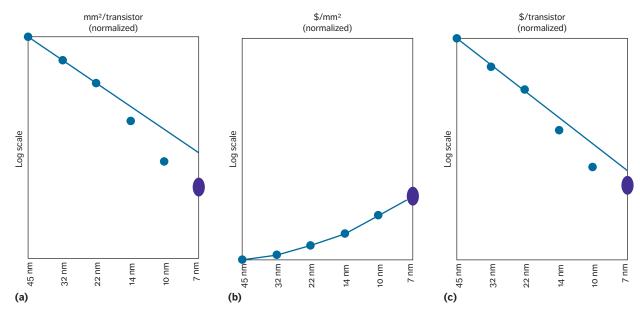

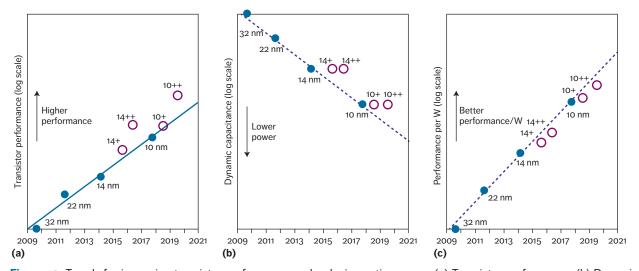

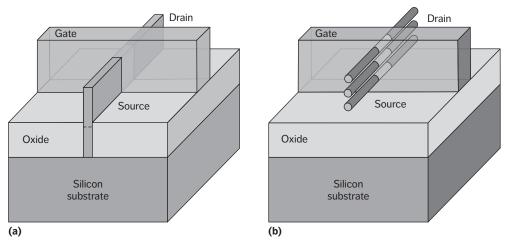

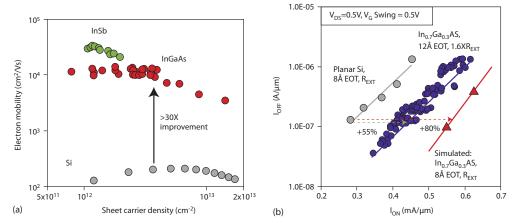

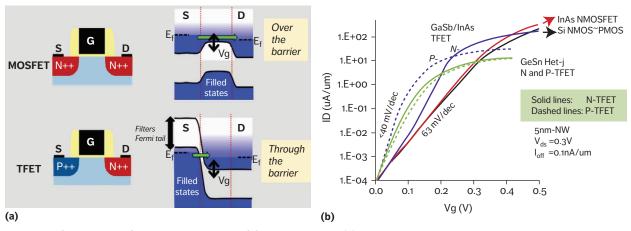

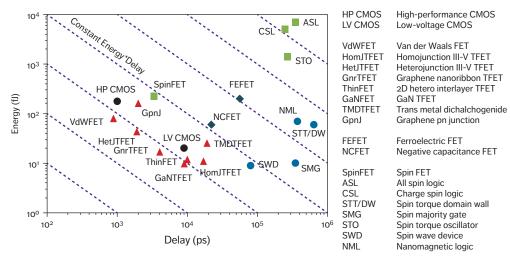

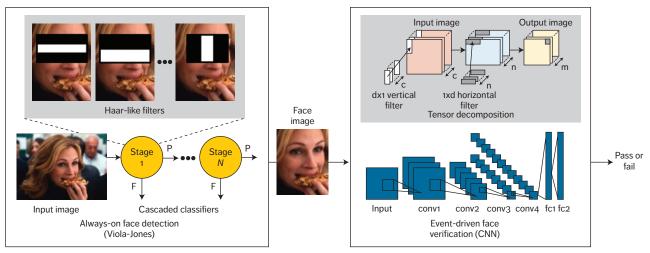

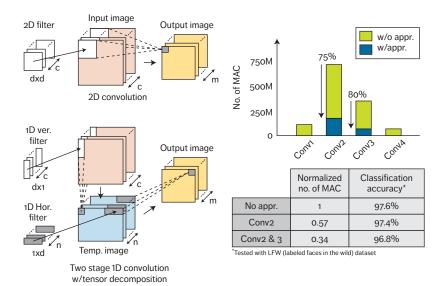

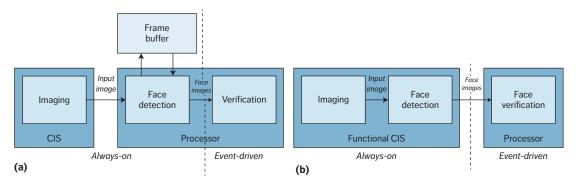

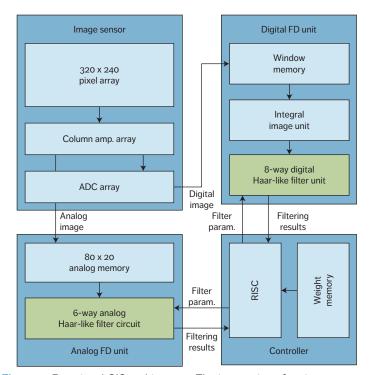

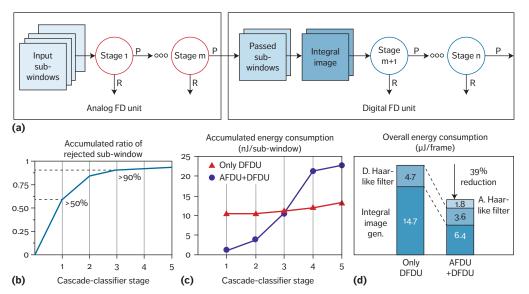

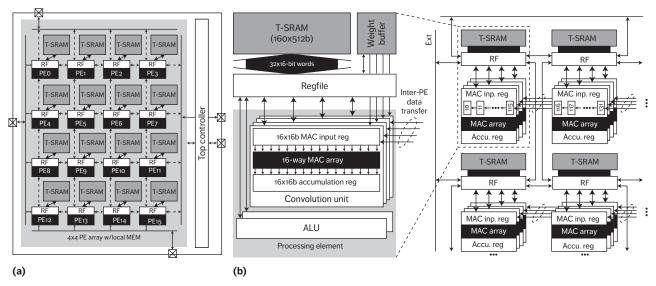

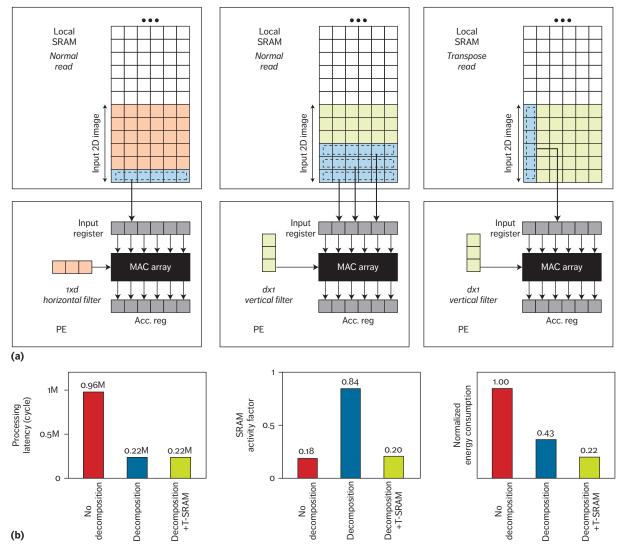

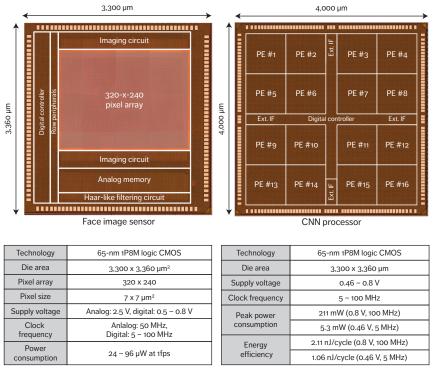

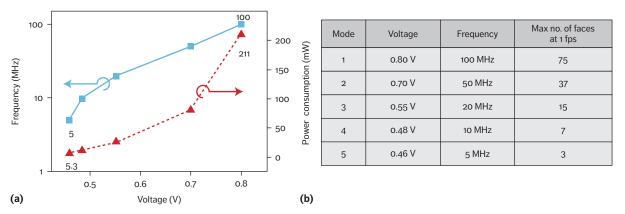

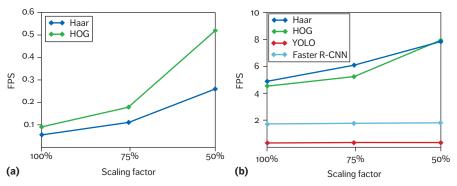

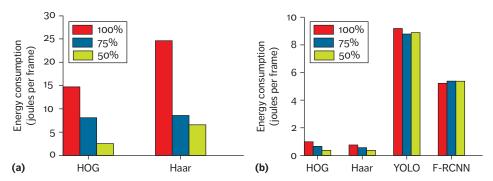

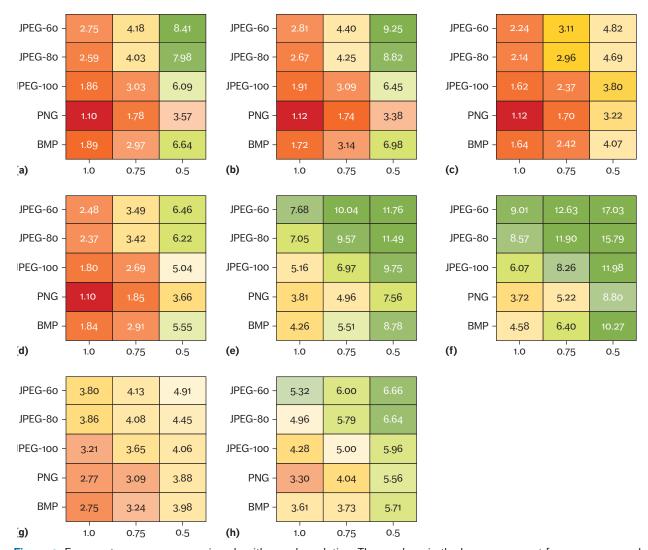

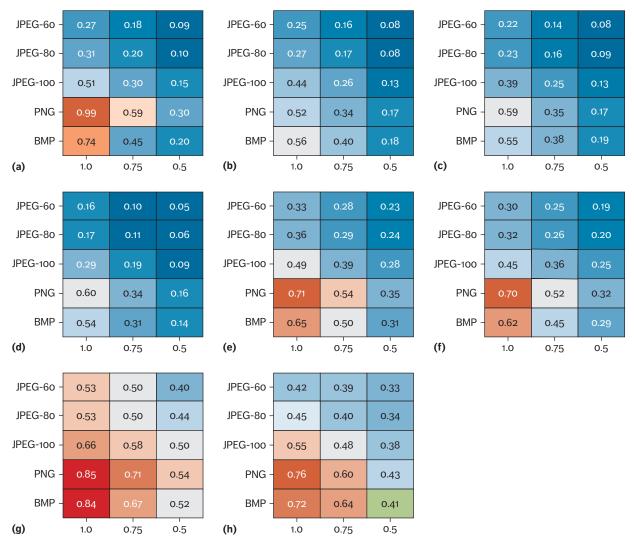

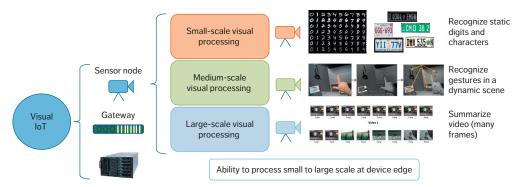

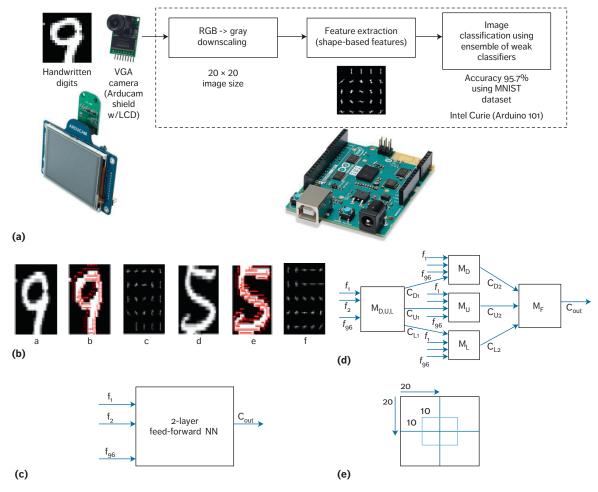

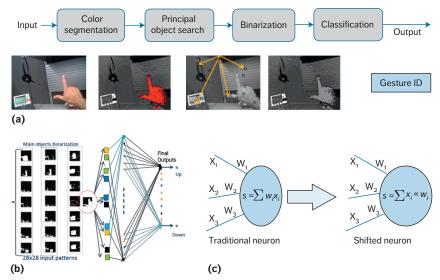

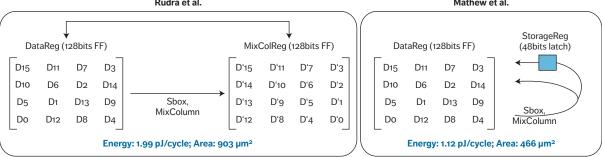

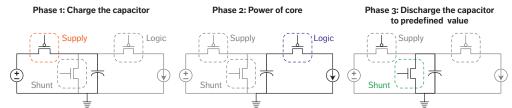

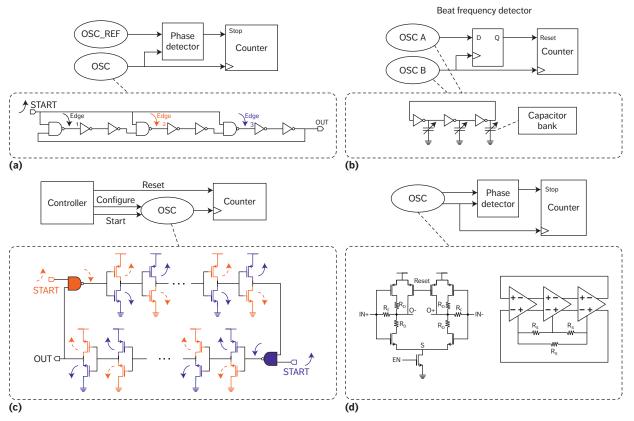

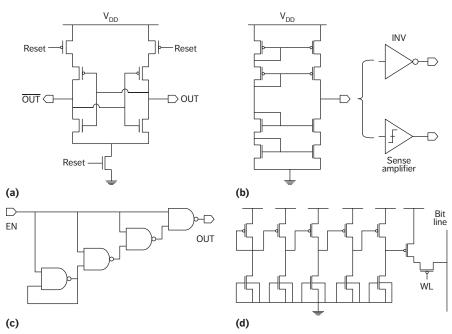

### **Beyond CMOS**