#### Estimation of Instantaneous Frequency Fluctuation in a Fast DVFS Environment Using an Empirical BTI Stress-Relaxation Model

Chen Zhou, Xiaofei Wang, Weichao Xu, \*Yuhao Zhu, \*Vijay Janapa Reddi, and <u>Chris H. Kim</u> University of Minnesota, Minneapolis, MN \*University of Texas at Austin

> {zhoux825, chriskim}@umn.edu www.umn.edu/~chriskim/

## Purpose

- Understand how BTI aging impacts frequency guardband in Dynamic Voltage Frequency Scaling (DVFS) systems

- Develop an efficient model for estimating BTI-induced frequency degradation under fast DVFS transients

# Outline

- Introduction to DVFS

- BTI Aging in DVFS Systems

- Proposed BTI Stress-Recovery Model

- Estimation of Frequency Fluctuation in a Real DVFS System

- Summary

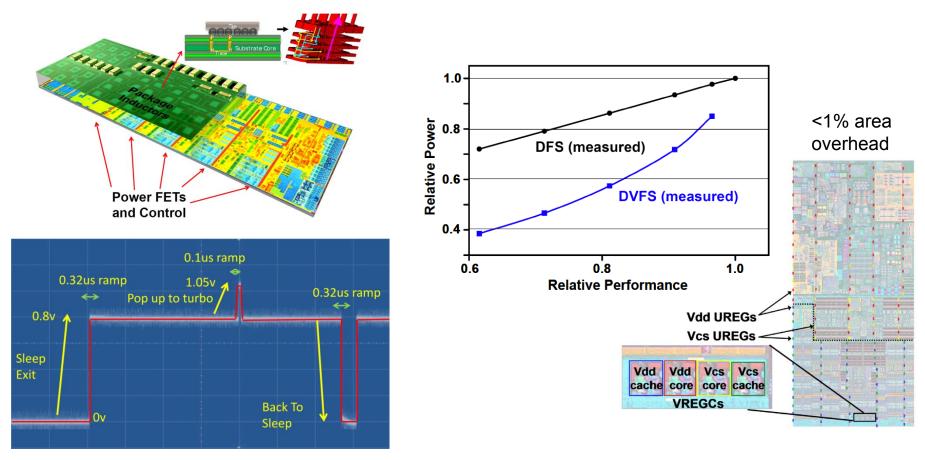

#### **DVFS Systems in ISSCC 2014**

22nm Intel Haswell processor N. Kurd, *et al.*, ISSCC, 2014 22nm IBM POWER8 processor Z. Toprak-Deniz, *et al.*, ISSCC, 2014

Latest trends: On-chip distributed VRM (fast transients, supply noise suppression), per-core DVS, NTV/Turbo

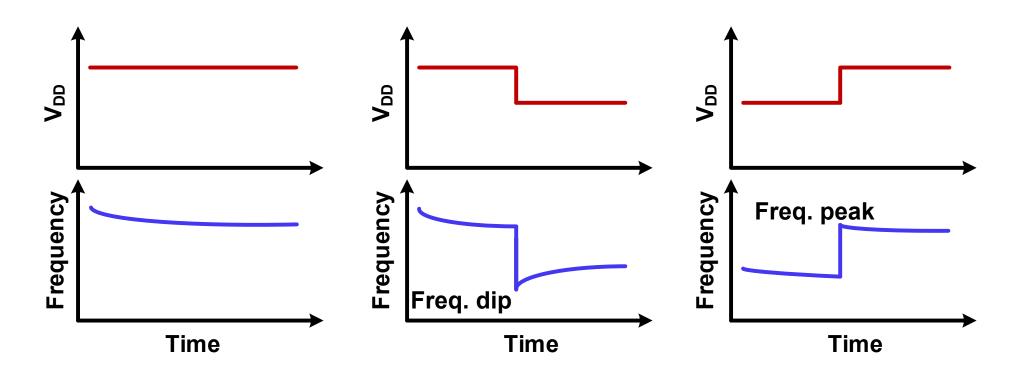

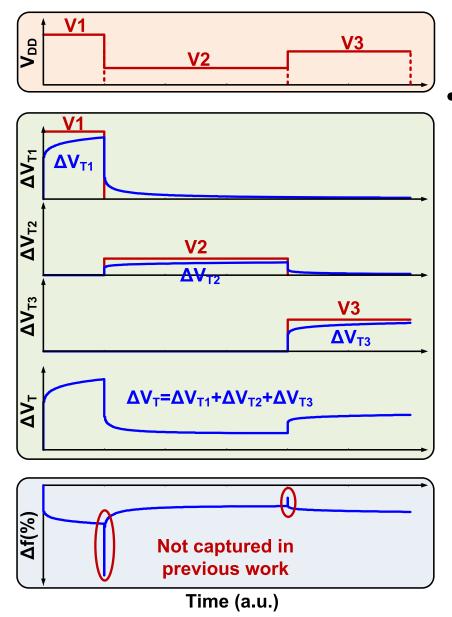

#### **Frequency Fluctuation in DVFS**

- Constant V<sub>DD</sub>: Frequency degrades with stress

- High V<sub>DD</sub> to low V<sub>DD</sub>: Freq. dips due to lower V<sub>DD</sub> followed by recovery

- Low  $V_{DD}$  to high  $V_{DD}$ : Freq. jumps and then degrades

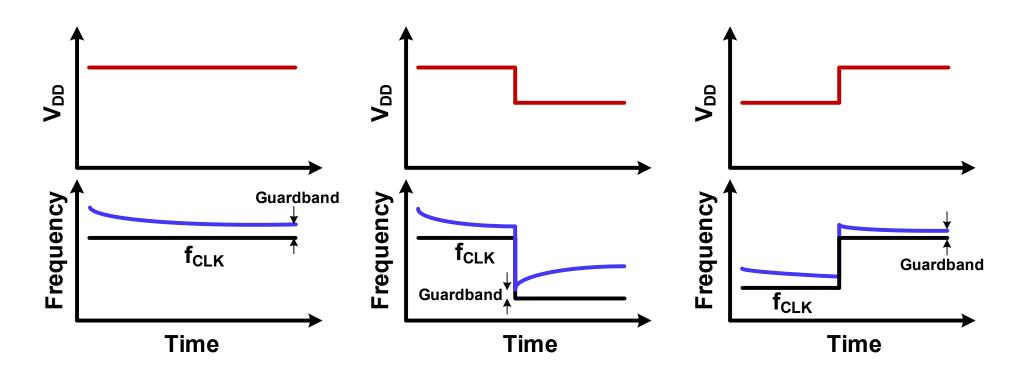

#### **Frequency Fluctuation in DVFS**

- Constant V<sub>DD</sub>: Frequency degrades with stress

- High V<sub>DD</sub> to low V<sub>DD</sub>: Freq. dips due to lower V<sub>DD</sub> followed by recovery

- Low  $V_{DD}$  to high  $V_{DD}$ : Freq. jumps and then degrades

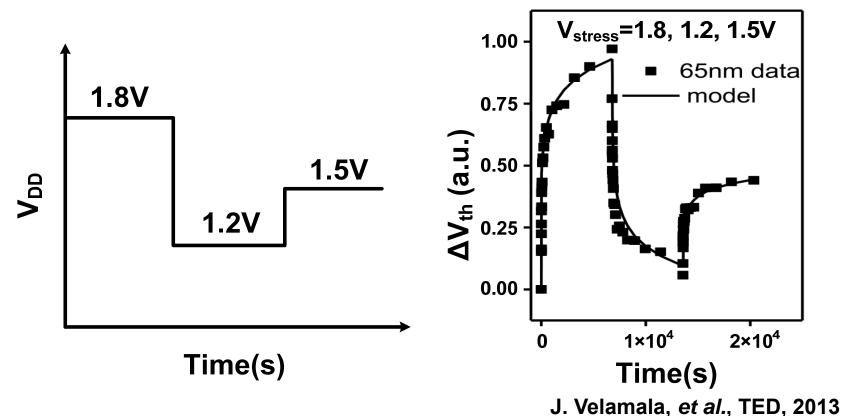

#### Previous Work on BTI Modeling under DFVS

- Limitations of prior work:

- Focus was on long term aging

- Frequency fluctuation in µs timescale was not considered

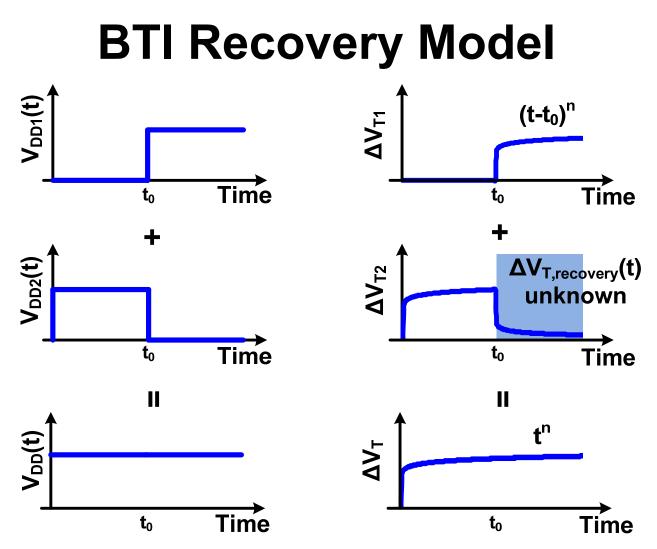

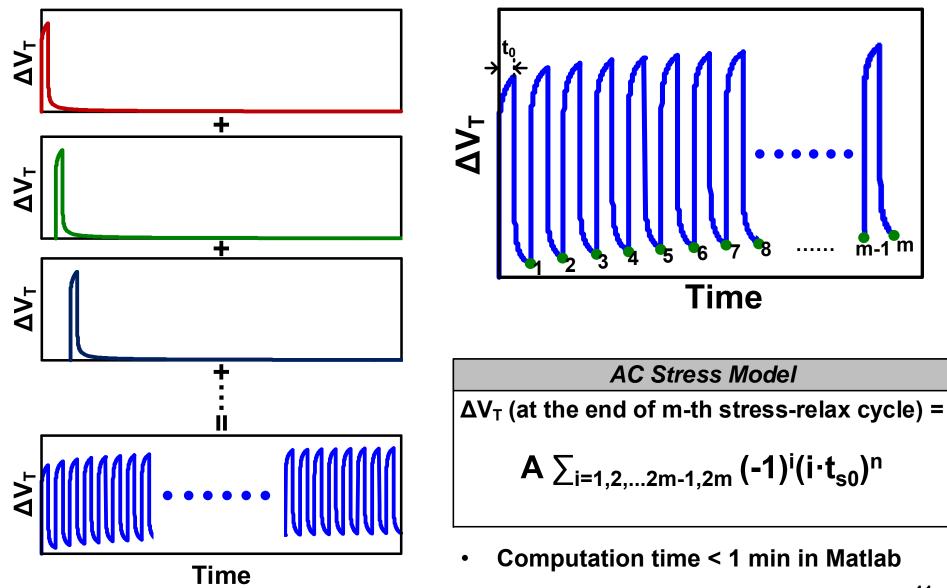

## **Modeling Approach using Superposition**

- Rationale for empirical superposition method :

- Complicated V<sub>DD</sub> trace can be broken down into multiple pulses

- Suitable for both longand short-term, DC and AC

- Computation is more efficient, short runtime

- Stress model: t<sup>n</sup> (power law)

- Recovery model derived from superposition property:  $\Delta V_{T,recovery}(t) = t^n - (t-t_0)^n$

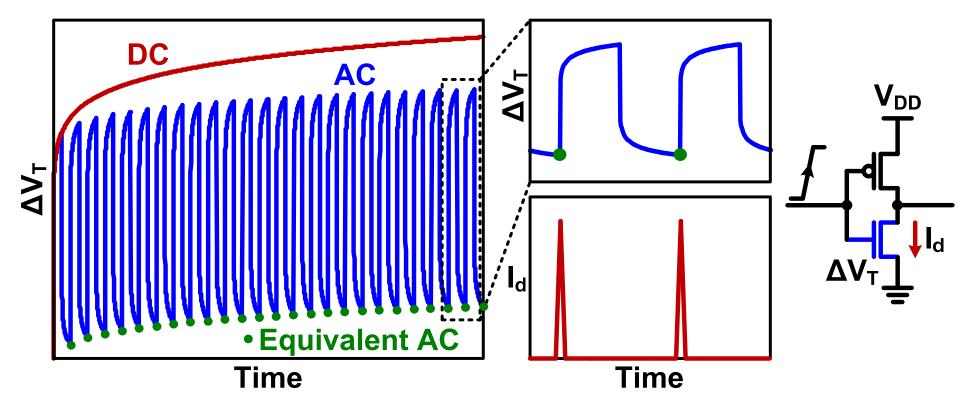

#### Incorporating Cycle-to-Cycle AC Stress

- Key observation: Transistor is in recovery mode just prior to switching

- Estimate lower envelope of the AC stress wave (only applicable to cycle-to-cycle AC stress)

#### **Equivalent AC Stress Model**

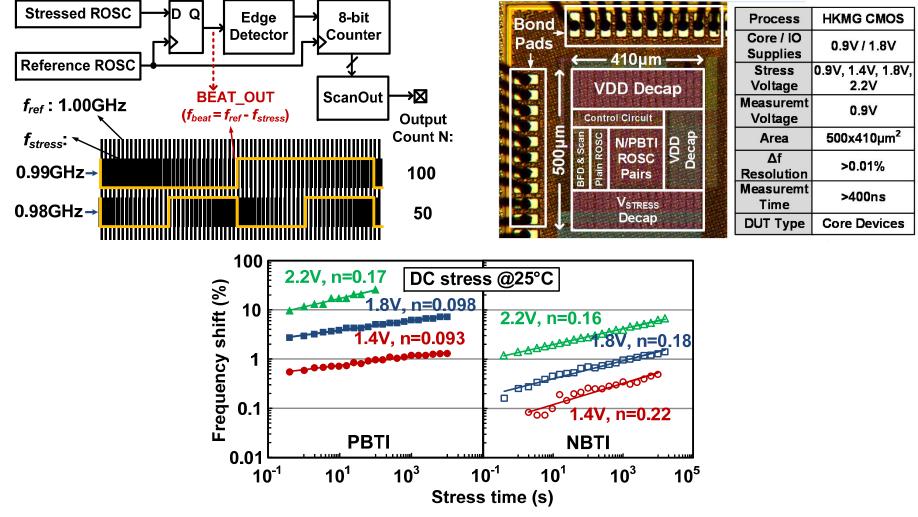

#### Extracting BTI Parameters from a 32nm HKMG Odometer Test Chip

Frequency shift measured using beat frequency method 12

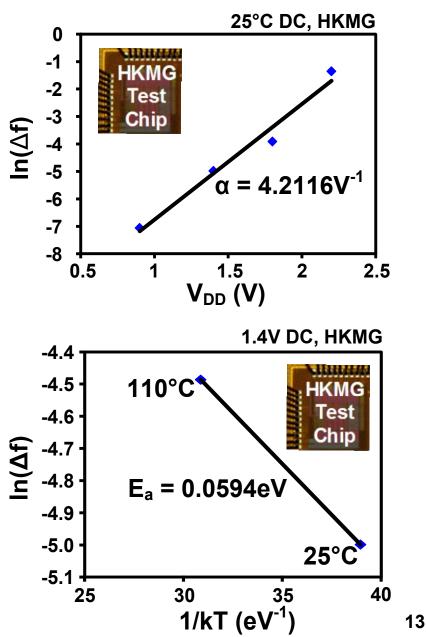

#### **Voltage and Temperature Accel. Factors**

$\Delta V_T$  vs.  $V_{DD}$

$$\Delta V_T(t) \propto e^{\alpha V_{DD}} \cdot t^n$$

$\Delta V_T$  vs. T

$$\Delta V_T(t) \propto e^{-\frac{E_a}{kT}} \cdot t^n$$

$$\frac{\Delta f}{f} = \frac{\Delta V_T}{V_{DD} - V_T}$$

Calculate voltage acceleration factor and thermal activation energy from measured data

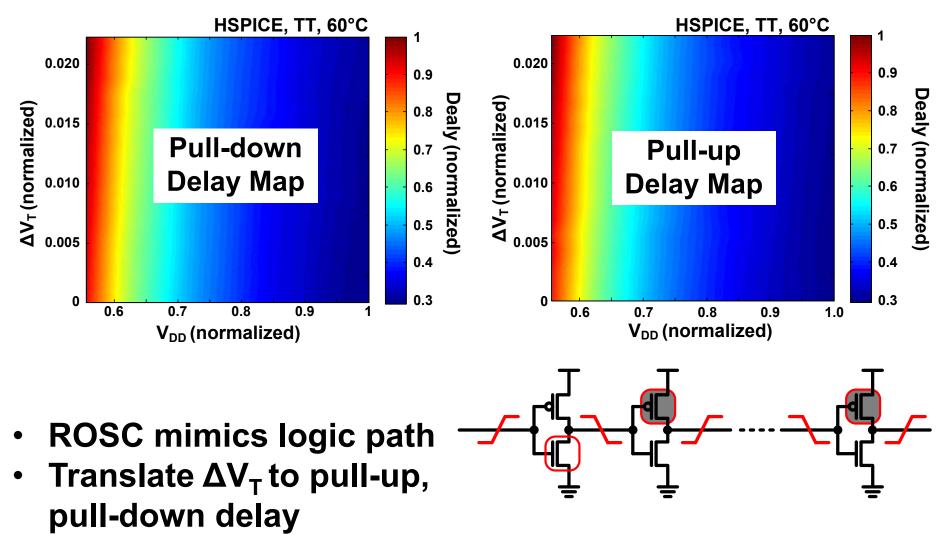

## Translating $V_T$ Shift to Delay Shift

**Pull-down Delay**

**Pull-up Delay**

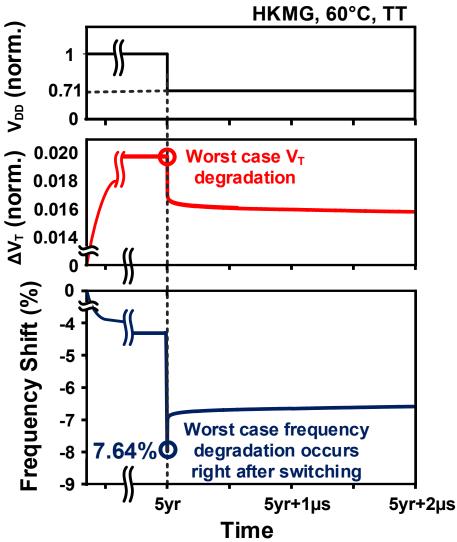

#### **Worst-case Scenario Example**

- Five years full  $V_{DD}$  DC stress  $\rightarrow$  low  $V_{DD}$  active mode

- 7.64% frequency dip immediately after switch

## Android Development Board for Collecting DVFS Traces

| AND A DIALOW AND A CONTRACT OF A DIALOW AND A | Processor                 | ARM Cortex A15    |

|----------------------------------------------------------------------------------------------------------------|---------------------------|-------------------|

|                                                                                                                | System                    | Samsung Exynos    |

|                                                                                                                |                           | 5410 SoC          |

|                                                                                                                | Process                   | 28nm              |

| Exynos 5410 SoC                                                                                                | Frequency                 | 0.8 – 1.8 GHz     |

|                                                                                                                | Voltage                   | 0.9 – 1.25 V      |

|                                                                                                                | Sense Resistor DVFS meas. | National Instr.   |

| Sense Resistor                                                                                                 |                           | DAQ               |

|                                                                                                                | Sampling                  | 1000 samples      |

|                                                                                                                | frequency                 | per second        |

|                                                                                                                | Linux kernel              | v 3.4.5           |

|                                                                                                                | Operating                 | Android v 4.2.2   |

|                                                                                                                | system                    | Allul Olu V 4.2.2 |

- V<sub>DD</sub> and operating frequency collected in real time

- Navigating websites, running benchmark applications

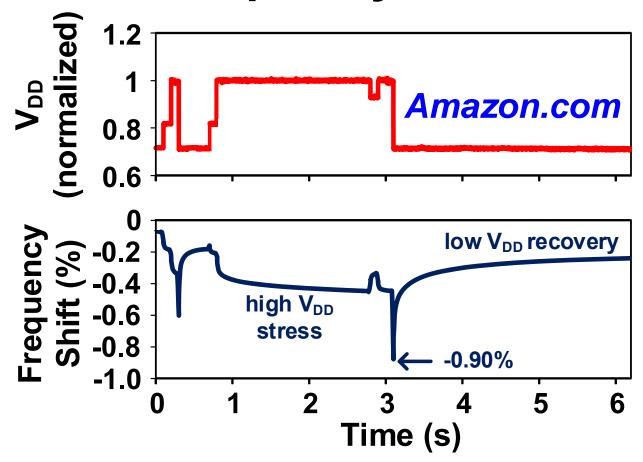

#### Sample Waveform and Estimated Frequency Shift

- High V<sub>DD</sub> duration: Freq. degrades with time

- Low V<sub>DD</sub> duration: Freq. shift dips and then recovers

#### **Applying Model to Other DVFS Traces**

- Worst case frequency dip

- 3D-raytrace: Δf=1.0% at t=6s when V<sub>DD</sub> drops by 29% after staying in high V<sub>DD</sub> mode for 5.8s

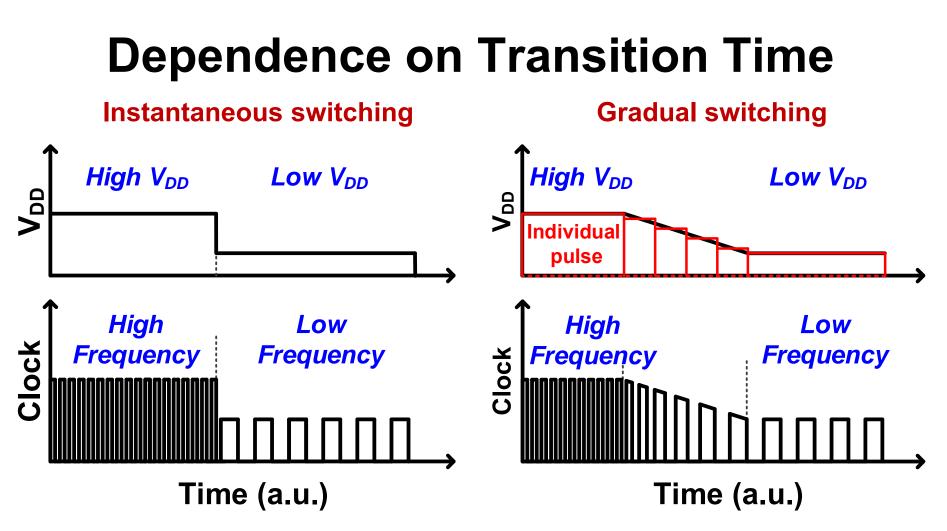

- Ramp voltage can be approximated as individual pulses with different heights

- Our empirical model can used to study the impact of ramp time on frequency shift dips

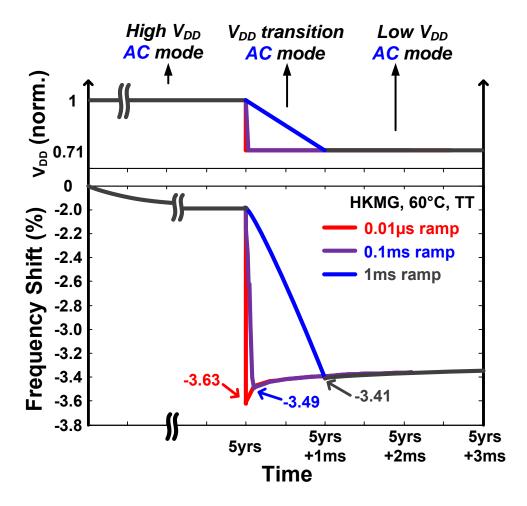

## Ramp Time vs. Frequency Shift Dip

- Ramp time: 0.01µs to 1ms  $\rightarrow \Delta f$  dip: -3.63% to -3.41%

- Explanation: Recovery kicks in before lowest V<sub>DD</sub> reached

## Summary

- An empirical BTI model for DVFS analysis developed

- A recovery model is derived from R-D stress model using superposition property

- Capable of handling complicated DVFS scenarios

- Short simulation time (< 1 minute using Matlab)</li>

- BTI induced frequency degradation estimated for the first time using real DVFS traces

- V<sub>DD</sub> traces for various benchmarks collected from an ARM Cortex A15 processor

- Frequency shift dips and peaks are estimated using proposed empirical model