# Deploying Dynamic Code Transformation in Modern Computing Environments

by

Vijay Janapa Reddi

B.S., Santa Clara University, 2003

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Master of Science Department of Electrical and Computer Engineering

2006

This thesis entitled: Deploying Dynamic Code Transformation in Modern Computing Environments written by Vijay Janapa Reddi has been approved for the Department of Electrical and Computer Engineering

Professor Daniel A. Connors

Dr. Robert S. Cohn

Professor Andrew Pleszkun

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline. Janapa Reddi, Vijay (M.S., Computer Engineering)

Deploying Dynamic Code Transformation in Modern Computing Environments

Thesis directed by Professor Daniel A. Connors

Dynamic code transformation systems are steadily gaining acceptance in computing environments for services such as program optimization, translation, instrumentation and security. Code transformation systems are required to perform complex and time consuming tasks such as costly program analysis and apply transformations (i.e. instrumentation, translation etc.) As these steps are applied to all code regions (regardless of characteristics), the *transformation overhead* can be significant. Once transformed, the remaining overhead is determined by the *performance of the translated code*. Current code transformation systems can only become part of mainstream computing only if these overheads are eliminated. Nevertheless, certain application and computing environments exist in which code transformation systems can be effectively deployed. This thesis identifies two such environments, persistence and mixed execution.

Persistence leverages previous execution characteristics to address the transformation overhead. This is accomplished by capturing the translated executions at the end of their first invocation. The captured executions are cached on disk for re-use. All subsequent invocations of the run-time system using the same application cause the system to reuse the cached executions. Since applications exhibit similar behavior across varying input data sets, this execution model successfully diminishes the transformation overhead across multiple invocations. Persistence in the domain of dynamic binary instrumentation is highlighted as an example.

Mixed execution accepts that the performance of the code generated by today's code transformation systems is in no position to compete with original execution times. Therefore, this technique proposes executing a mix of the original and translated code sequences to keep the translated code performance penalties within bounds. This execution model is a more effective alternative to pure Just-in-Time compiler-based code transformation systems, when low overheads and minimal architectural perturbation are the critical constraints required to be met. A dynamic compilation framework for controlling microprocessor energy and performance using this model is presented in light of its effectiveness and practicality.

## Contents

# Chapter

| 1        | Intro                                                                            | oductio                                               | n                                                         | 1  |  |  |  |  |

|----------|----------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|

| <b>2</b> | Cha                                                                              | naracteristics of dynamic code transformation systems |                                                           |    |  |  |  |  |

|          | 2.1                                                                              | Applic                                                | eations                                                   | 6  |  |  |  |  |

|          |                                                                                  | 2.1.1                                                 | Optimization                                              | 6  |  |  |  |  |

|          |                                                                                  | 2.1.2                                                 | Translation                                               | 8  |  |  |  |  |

|          |                                                                                  | 2.1.3                                                 | Instrumentation                                           | 9  |  |  |  |  |

|          |                                                                                  | 2.1.4                                                 | Security                                                  | 10 |  |  |  |  |

|          | 2.2                                                                              | Funda                                                 | mental barriers                                           | 11 |  |  |  |  |

|          | 2.3 Framework used to delineate and address the fundamental barrier $\therefore$ |                                                       |                                                           |    |  |  |  |  |

| 3        | Cha                                                                              | llenges                                               | faced by state of the art run-time transformation systems | 14 |  |  |  |  |

|          | 3.1                                                                              | Transformation cost                                   |                                                           |    |  |  |  |  |

|          |                                                                                  | 3.1.1                                                 | Start-up (initialization) transformation overhead         | 16 |  |  |  |  |

|          |                                                                                  | 3.1.2                                                 | Infrequently executed code                                | 19 |  |  |  |  |

|          |                                                                                  | 3.1.3                                                 | Code transformation components                            | 19 |  |  |  |  |

|          | 3.2                                                                              | .2 Translated code performance                        |                                                           |    |  |  |  |  |

|          |                                                                                  | 3.2.1                                                 | Code layout                                               | 22 |  |  |  |  |

|          |                                                                                  | 3.2.2                                                 | Varying branch target instructions                        | 25 |  |  |  |  |

|          |                                                                                  | 3.2.3                                                 | Maintaining application transparency                      | 27 |  |  |  |  |

|   | 3.3  | 3 Execution environment effects on run-time systems                  |                                                               |    |  |  |  |

|---|------|----------------------------------------------------------------------|---------------------------------------------------------------|----|--|--|--|

|   |      | 3.3.1                                                                | Compiler vendors                                              | 28 |  |  |  |

|   |      | 3.3.2                                                                | Compiler optimizations                                        | 30 |  |  |  |

|   |      | 3.3.3                                                                | Compiler consequences on dynamic optimization                 | 31 |  |  |  |

|   |      | 3.3.4                                                                | Machine resources                                             | 33 |  |  |  |

|   |      | 3.3.5                                                                | Everyday application environment                              | 39 |  |  |  |

| 4 | Exp  | loiting                                                              | persistent characteristics to address transformation overhead | 41 |  |  |  |

|   | 4.1  | Execu                                                                | tion path variance across different inputs                    | 42 |  |  |  |

|   | 4.2  | Applie                                                               | cations of persistence                                        | 44 |  |  |  |

|   | 4.3  | A per                                                                | sistent run-time system                                       | 45 |  |  |  |

|   |      | 4.3.1                                                                | Challenges                                                    | 47 |  |  |  |

|   |      | 4.3.2                                                                | Persistence in a binary instrumentation system                | 49 |  |  |  |

|   |      | 4.3.3                                                                | Overhead reduction over the lifetime of programs              | 50 |  |  |  |

|   |      | 4.3.4 Start-up cost reduction                                        |                                                               |    |  |  |  |

|   |      | 4.3.5                                                                | Persistent cache analysis                                     | 54 |  |  |  |

| 5 | Miti | gating                                                               | the translation overhead via mixed execution                  | 57 |  |  |  |

|   | 5.1  | Code                                                                 | splicing                                                      | 58 |  |  |  |

|   |      | 5.1.1                                                                | Limitations                                                   | 61 |  |  |  |

|   |      | 5.1.2                                                                | Methodology                                                   | 63 |  |  |  |

|   | 5.2  | 2 Addressing a rising concern with run-time code transformation: pow |                                                               |    |  |  |  |

|   |      | management                                                           |                                                               |    |  |  |  |

|   |      | 5.2.1                                                                | A run-time dynamic voltage and frequency scaling optimizer    | 68 |  |  |  |

|   |      | 5.2.2                                                                | Challenges                                                    | 68 |  |  |  |

|   |      | 5.2.3                                                                | Experimental framework                                        | 69 |  |  |  |

|   |      | 5.2.4                                                                | Methodology                                                   | 70 |  |  |  |

|   |      | 5.2.5                                                                | RDO baseline overhead                                         | 71 |  |  |  |

vi

|   | 5.2.6      | RDO performance | <br> | <br> | <br>. 73 |

|---|------------|-----------------|------|------|----------|

| 6 | Summary a  | and conclusion  |      |      | 75       |

| В | ibliograph | y               |      |      | 78       |

vii

## Tables

### Table

| 5.1 | Systems  | where | the | mixed | execution | mode | and | JIT-based | run-time sys- |    |

|-----|----------|-------|-----|-------|-----------|------|-----|-----------|---------------|----|

|     | tems app | oly   |     |       |           |      |     |           |               | 64 |

# Figures

## Figure

| 2.1 | Overview of (a) interpretation and (b) Just-In-Time (JIT) based dynamic     |    |

|-----|-----------------------------------------------------------------------------|----|

|     | optimization systems.                                                       | 6  |

| 2.2 | Overview of the run-time system utilized as the evaluation framework        | 13 |

| 3.1 | Performance of the translated code relative to the original program. Ex-    |    |

|     | ecution time bars of the application running under the run-time system      |    |

|     | are stacked to show the distribution of the time spent generating the       |    |

|     | translated code versus executing the translated code                        | 15 |

| 3.2 | Time spent in the run-time code transformation system while executing       |    |

|     | the SPEC2K benchmark suite. Every black line represents the compila-        |    |

|     | tion of a new code sequences. Space between adjacent black lines indicates  |    |

|     | time being spent in already compiled code paths                             | 17 |

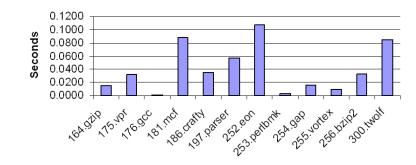

| 3.3 | Average time between requests from the run-time system's virtual machine.   | 18 |

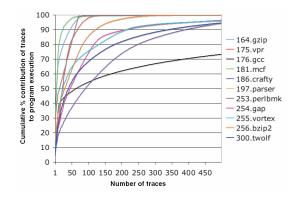

| 3.4 | Cumulative percentage of the number of traces that dominate program         |    |

|     | execution.                                                                  | 19 |

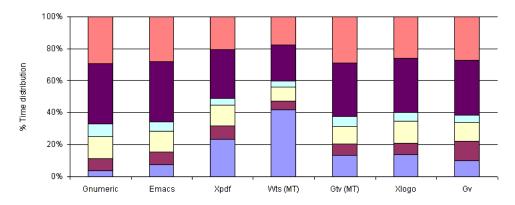

| 3.5 | Distribution of time spent in components of the run-time system             | 20 |

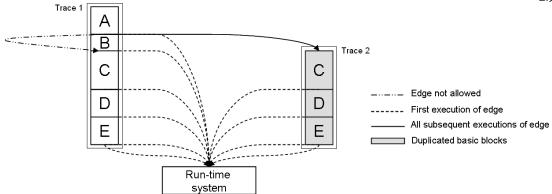

| 3.6 | Code duplication that results as a result of speculative fetching and trace |    |

|     | formation.                                                                  | 23 |

| 3.7 | Percentage of all the translated application code utilized by the run-time  |    |

|     | system.                                                                     | 24 |

| 3.8  | Percentage increase in instruction TLB misses when running the appli-                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | cations under the control of the run-time system                                                                                                            | 26 |

| 3.9  | Indirect branch predictions                                                                                                                                 | 27 |

| 3.10 | Performance impact based on the compiler used to generate the binaries.                                                                                     | 29 |

| 3.11 | Effects of compiler optimizations on the performance of code transforma-                                                                                    |    |

|      | tion and translated code execution time                                                                                                                     | 31 |

| 3.12 | Comparison of dynamic optimization (loop unrolling and inlining) on                                                                                         |    |

|      | binaries generated using different compilers: (a) Gcc and (b) Intel (Icc).                                                                                  | 32 |

| 3.13 | Run-time system performance observed under different processor/system                                                                                       |    |

|      | resources                                                                                                                                                   | 34 |

| 3.14 | Performance of the run-time system utilizing the software based return                                                                                      |    |

|      | address prediction stack                                                                                                                                    | 38 |

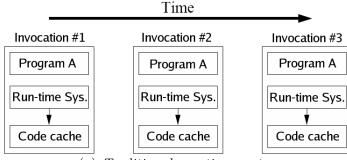

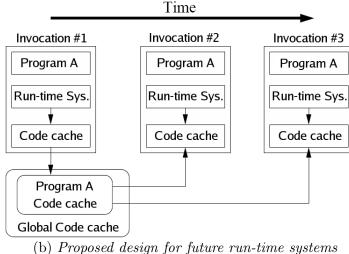

| 4.1  | (a) Current model applied by dynamic code transformation systems where                                                                                      |    |

| 1.1  | they target accomplishing their task only within the current instance of                                                                                    |    |

|      | execution (b) Proposed design for run-time systems in the future that                                                                                       |    |

|      | exploit execution (b) i roposed design for run-time systems in the future that<br>exploit execution characteristics across multiple invocations of the same |    |

|      |                                                                                                                                                             | 42 |

| 4.0  | program                                                                                                                                                     | 42 |

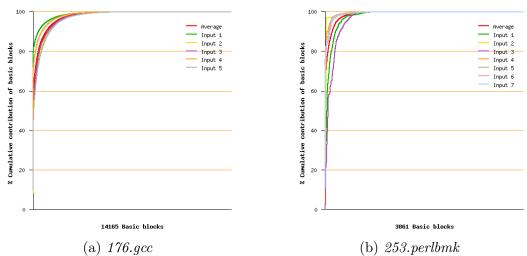

| 4.2  | Cumulative contribution to program execution by basic blocks for 176.gcc                                                                                    | 49 |

| 4.0  | and 253.perlbmk across all their SPEC2K reference input data sets                                                                                           | 43 |

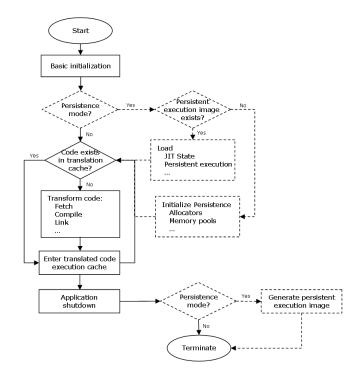

| 4.3  | Overview of a persistent code transformation system. Dotted lines indi-                                                                                     | 10 |

|      | cate Persistence specific states.                                                                                                                           | 46 |

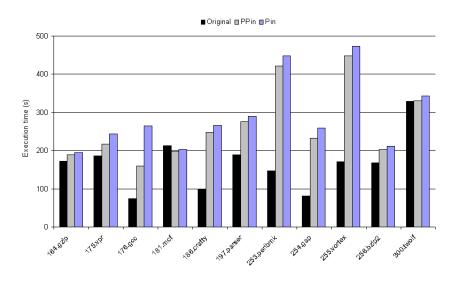

| 4.4  | Persistent Pin's performance in comparison to native and Pin's perfor-                                                                                      |    |

|      | mance                                                                                                                                                       | 51 |

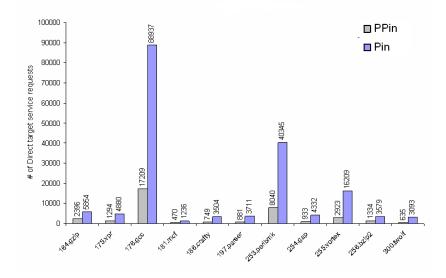

| 4.5  | Pin service requests from the translated code                                                                                                               | 52 |

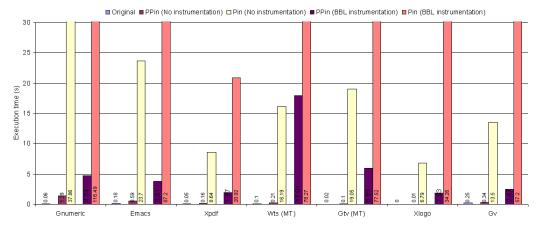

| 4.6  | Execution time for BBL instrumentation using Persistent Pin vs. Pin.                                                                                        |    |

|      | Percentage improvements of PPin over Pin are shown                                                                                                          | 53 |

| 4.7 | Execution time of Persistent Pin vs. Pin for BBL instrumentation of           |    |

|-----|-------------------------------------------------------------------------------|----|

|     | everyday applications. Applications were started and immediately shut-        |    |

|     | down, this is the worst case scenario and illustrates the benefits of caching |    |

|     | cold code.                                                                    | 54 |

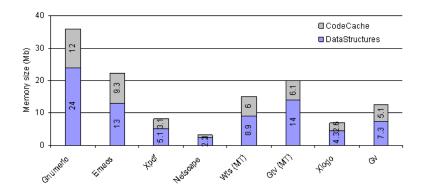

| 4.8 | Persistent cache sizes.                                                       | 55 |

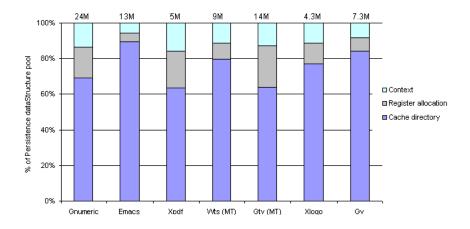

| 4.9 | Breakdown of the data structures persistent cache                             | 56 |

| 5.1 | Time to collect the dynamic execution count of all functions executed         | 60 |

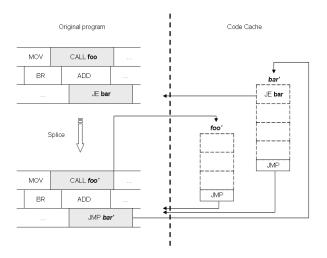

| 5.2 | Using code splicing as a means of transferring program control from the       |    |

|     | application to the code cache sequences. The gray shaded boxes are $5$        |    |

|     | byte x86 instructions, so they are patchable                                  | 64 |

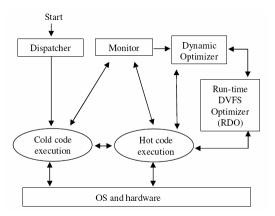

| 5.3 | Overall system structure showing the operation and interactions among         |    |

|     | different components of a dynamic compiler DVFS optimization system.          | 68 |

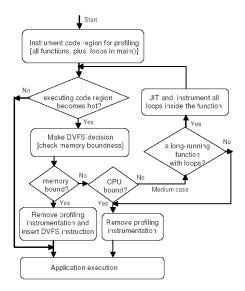

| 5.4 | Operation flow graph of the run-time dynamic voltage and frequency            |    |

|     | scaling system.                                                               | 71 |

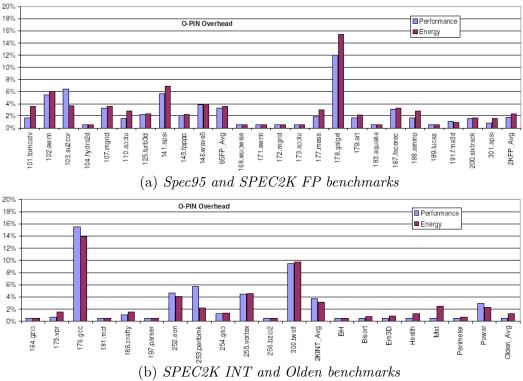

| 5.5 | Performance and energy overhead for (a) Spec95 and SPEC2K FP and              |    |

|     | (b) SPEC2K INT and Olden benchmarks resulting from the RDO system             |    |

|     | without applying DVFS optimizations                                           | 72 |

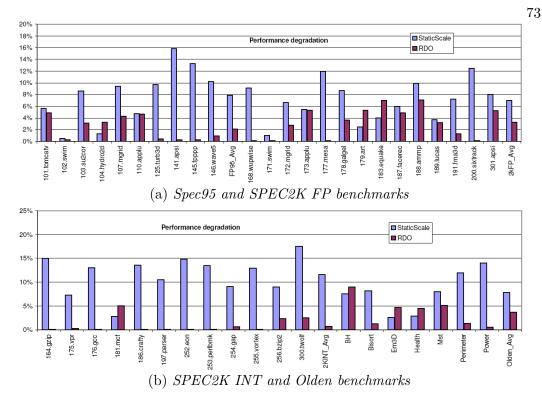

| 5.6 | Performance degradation because of running RDO along side the appli-          |    |

|     | cation                                                                        | 73 |

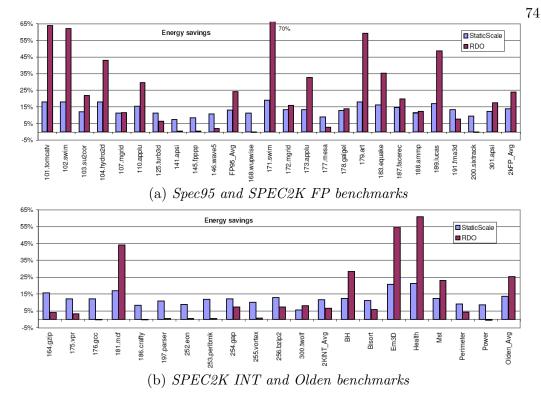

| 5.7 | Energy savings achieved by the run-time dynamic voltage and frequency         |    |

|     | scaling optimizer                                                             | 74 |

#### Chapter 1

#### Introduction

Dynamic code transformation systems have the potential to impact the design and use of modern computer systems since they can provide a number of services at run-time, such as instrumentation, optimization, translation and security. These systems have an inherent advantage over static techniques, as they can collect and exploit run-time execution characteristics. The information collected can be used to adapt the execution of the target application. However, since the execution of current run-time system is generally interleaved with the execution of the application, there is a substantial overhead penalty. In the context of performance analysis and program behavior tools, the overhead of a dynamic code transformation system may be acceptable. Nonetheless, execution penalty is a major barrier towards deploying run-time code transformation in computing systems, specifically in use in large-scale application environments.

While prior works provide considerable insight into the potential of run-time adaptation of applications, such work provides only limited insight into the elements that are vital to the practical deployment of traditionally-proposed run-time systems. Other code transformation models exist such as the use of multi-core hardware and specialpurpose architecture-support for evaluating the full potential of code transformation systems; however this thesis centers on the deployment of run-time transformation in a software-based domain. In this context, program behavior and the design of the code transformation system have the largest impact on the execution overhead incurred by an application under a run-time system. The resulting overhead is an aggregate of the (1) transformation cost and (2) the penalty due to the poor translated code performance.

Transformation overhead is determined by the complexity of run-time analysis and transformation components applied to the code (run-time compiler, register allocator, optimizer, cache manager etc.). Likewise, the overhead of each system component is not fixed, but depends on the run-time characteristics of the application. For instance, at startup, most programs have tremendous amounts of code that are executed once or only a few times. A dynamic code transformation system will not be able to amortize the run-time overhead costs for these code sequences. Run-time systems rely on the repeated execution of the translated code sequences to amortize their overhead.

The performance of the translated code is controlled by factors such as whether optimization is applied or instrumentation code is added during transformation. In addition, the code generated by a run-time system often varies from the original instruction stream to make sure that the application remains under the control of the run-time system at all times. Likewise, care can also be taken to ensure that the application is not perturbed by the presence of the run-time system. These changes to the instruction stream often contribute to a significant amount of overhead.

It is imperative for researchers to understand the resulting transformation and translated code performance overheads as they are currently beyond tolerable. Only when run-time overheads break even with original execution times can current code transformation systems become integrated into mainstream computing environments. However, certain application and computing environment characteristics exist that can still benefit from the deployment of current code transformation systems.

This thesis presents two models of code transformation that exploit unique computing scenarios: *persistence* and *mixed execution*. Both models leverage aspects of an application and run-time system dealing with execution overheads. These executions models are evaluated in a state-of-the-art Just-In-Time (JIT)-based code transformation system to mitigate the transformation and translated code performance penalties. The conclusion made, based on their evaluations, is that existing dynamic code transformation systems can be deployed into mainstream computing environments when specific execution properties and conditions exist.

Persistence leverages an application facet; applications exhibit very similar execution paths across varying input data sets. The persistent code-transformation model mitigates transformation overhead across executions by caching translated executions. Translated code sequences, captured at the end of the first execution, are cached on disk for re-use. All subsequent invocations of the run-time system using the same application cause the system to reuse the cached executions. The Persistence execution model in the domain of dynamic binary instrumentation is highlighted as an example using the Pin [31] framework. The approach successfully mitigates the overhead of SPEC2K applications, by as much as 25%, and over 90% for everyday applications like web browsers, display rendering systems, and spreadsheet programs.

Mixed execution addresses a challenging aspect of run-time systems which is poor performance of translated code. The motivation behind this execution model is that code executed as a mix of the original and transformed code sequences can avoid many pitfalls of a fully translated code execution sequence such as the removal of costly return and indirect branch handling sequences. Therefore, mixed execution is a practical alternative to pure Just-In-Time compiler-based code transformation systems when extremely low overheads and minimal architectural perturbation are critical constraints. The mixed execution model is evaluated in the Pin [31] run-time system addressing the rising concern of microprocessor power consumption. It exhibits minimal overheads, which are as low as  $\sim 4\%$ . Consequently, the run-time power-saving optimizer successfully achieves energy savings up to 70% for applications in the SPEC2K benchmark suite, with an  $\sim 0.5\%$  performance degradation. The remainder of this thesis is organized as follows: Section 2 presents background into run-time code transformation systems and describes their fundamental barriers. Section 3 characterizes the various challenges faced by these systems. Two distinct models of addressing these barriers are proposed and evaluated in Section 4 and Section 5. Finally, Section 6 draws a summary of the work accomplished in this thesis.

#### Chapter 2

#### Characteristics of dynamic code transformation systems

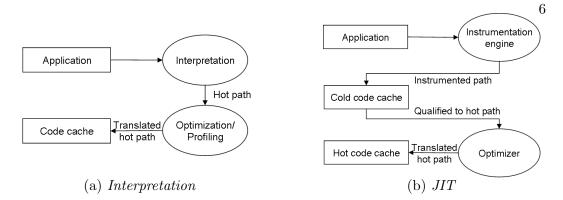

Existing dynamic code transformation systems rely on a Just-In-Time (JIT) compiler, or an interpretation system to follow the dynamic execution path of a program. Figure 2.1 illustrates how dynamic optimization is applied in either of the two methods of dynamic code transformation. In the Interpretation model, shown in Figure 2.1 (a), instructions are emulated while at the same time profile information is gathered inside the interpreter. Interpretation's advantage is that it is relatively simple to implement, especially in the case of software translation systems [26, 14] where the input ISA is different than the host ISA. However, interpretation generally is a slow process. In the JIT model, shown in Figure 2.1 (b), a run-time compiler is utilized due to its inherent ability to generate more efficient code sequences. Since all JIT approaches work on the granularity of at least a basic block, there is more scope for run-time optimizations. Such is not the case in the interpretation model since the scope is limited to just one instruction.

Generally, these systems disrupt the target program execution with multiple steps to initiate, monitor, and consider every code sequence for optimization/transformation. As the primary goal of these systems is to perform their task under execution time constraints, implementing practical systems based on these run-time models can be challenging in certain commercial and scientific environments that contain a substantial

Figure 2.1: Overview of (a) interpretation and (b) Just-In-Time (JIT) based dynamic optimization systems.

number of unique execution paths.

#### 2.1 Applications

This section presents background into existing run-time code transformation systems. The section first motivates the reason for performing the tasks at run-time versus at static compile time, followed by referrals to seminal works.

#### 2.1.1 Optimization

For years, the steadily growing clock speed of new processors has been relied upon to consistently deliver increasing performance for a wide range of applications. However, processor frequency scaling has stalled, driving microprocessor companies to investigate adding value through alternative technologies. To continue making gains in system performance, the overall system must dynamically adjust resource allocations to meet system needs. Unfortunately, existing systems do not provide such support. Without such support, static compilers, due to their inherent limitations, fail to realize the interaction between the hardware and application the code. In fact, aggressive compiletime optimization may even lower performance [46] when run-time characteristics and architecture resource constraints are not accurately addressed. Overcoming such issues involves embracing new architecture and software ideas, rather than simply attacking the problem by scaling hardware resources. As such, the need for run-time system support to adapt and optimize application behavior to hardware resources is increasing across each generation of emerging systems.

Taking advantage of the run-time behavior has been the motivation behind many recent works in the area of dynamic optimization (code transformation) [3, 6, 11, 29]. Generally, dynamic optimization refers to the process of modifying an application binary at run-time to promote desirable execution characteristics, such as high performance [6, 11, 3], low power [38, 44], or managed resource consumption [21]. Traditional dynamic optimizers first observe run-time characteristics to determine frequently executed sequences of code for performing optimizations within a given instance of execution. These sequences span procedure boundaries as well as cross into shared libraries and therefore have more potential for optimization.

There are several successful implementations of dynamic optimization systems such Dynamo [3], DynamoRIO [6], Mojo [11], DELI [13], and ADORE [29]. DynamoRIO, Mojo and DELI are examples where execution is initially done from a code cache where code is being monitored for optimization opportunities. Once an execution threshold metric (hot code detection) is exceeded, the systems go into code specialization mode of laying out a single-entry multiple-exit code sequence for the detected hot code region. The threshold identification metrics rely on software mechanisms that promote code from the initial cache to the optimized cache. DynamoRIO[6], an extension of Dynamo, supports applications in the Windows and Linux environments. These two optimizer infrastructures primarily focus on reducing the execution time of the application by identifying hot sections of the code and optimizing them to make the programs run more efficiently. The general performance improvement technique is centered on code layout optimizations. ADORE [29] is a dynamic optimizer that uses the hardware performance monitoring (HPM) system of a processor to detect hot code sequences and memory bottlenecks. The hardware information replaces the need for dynamic instrumentation and significantly lowers the overhead of the run-time code transformation system. ADORE is best known for dynamically deploying software prefetch instructions through the run-time identification of cache bottlenecks.

Feedback-directed optimization (FDO) also falls into the domain of optimization. It describes any technique that automatically alters a program's execution based on the run-time execution tendencies observed in current or previous runs. A good overview of the techniques and challenges of FDO are presented in [40]. Feedback-directed optimization tools such as Spike [12] and Vulcan [41] are static post-link optimizers that can statically optimize application binaries in response to user input and data patterns. Relatedly, Ispike [30] utilizes performance counters available on the Intel Itanium Architecture to automate the optimization between runs. The term *continuous optimization* has also emerged and is centered on performing continuous profiling, and therefore optimizing a program across multiple invocations. DCPI [1] is an example of such a system which continually samples a hardware performance monitoring unit to collect profiles. Kistler [28] explores a similar framework using hardware to collect profiles and continuously optimize programs between different runs.

#### 2.1.2 Translation

Related to dynamic optimization, translation systems facilitate the execution of binaries compiled for one Instruction Set Architecture (ISA) to execute on a different ISA. This is an effective means for companies to migrate from one ISA to another while maintaining backward compatibility.

With the recent announcement that Apple Computer will ship systems with Intel chips using Transitive's Rosetta translation software (to convert PowerPC applications to x86 at run-time) [33], code transformation systems have moved into the mainstream and are no longer an impractical full-system deployment strategy. IA32EL [4], HP- Aries [48], Daisy [14], Transmeta's CMS [26] and FX!32 [19] are other such translation systems. All of these systems with the exception of FX!32 are JIT based translation systems. FX!32 translates code from the x86 architecture to the Alpha architecture. It profiles the x86 application as it is emulated; afterward, the profile is used to generate optimized native code from the translated x86 code generated during the run. Future invocations utilize the native code, eliminating the full cost of performing profiling and transformation at execution time.

#### 2.1.3 Instrumentation

Understanding application characteristics for debugging or performance evaluation on systems is important to ensure that binaries compiled and shipped to customers function correctly and operate at peak performance. Applications can be analyzed at various stages of their creation - source code, link, or run-time. With the growing complexity of everyday software systems, the method chosen for introspection is critical to effectively and efficiently study the application behavior.

Source code instrumentation is extremely time consuming since the code has to be explicitly added/removed by editing the original program files. This form of instrumentation by definition requires the application source code. This requirement makes it an impractical approach in certain circumstances. Post-link and run-time instrumentation systems work at the binary level. They are classifiable into static or dynamic approaches.

The static approach relies on rewriting the object or executable file with the required instrumentation, thereby generating a new instrumented executable. Most static tools suffer from tool-chain dependence which requires the cooperation of the compiler and/or the linker when the binary is created. Dynamic instrumentation is a more effective and practical approach of instrumenting a binary since it imposes no special requirements.

Dynamic binary instrumentation systems are widely accepted and used as a means of characterizing program behavior for performance, code coverage and program correctness. They are also applicable in payload delivery and target function replacement [24].

Dynamic binary instrumentation is implementable either via (1) binary modification or (2) the recompilation of the application at run-time. Binary modification relies on using probes/trampolines which overwrite the original program instructions to invoke special code that handles the process of instrumenting the application code. The latter does not touch the original code. Instead, it decodes the original instructions and encodes them into a separate area of memory commonly referred to as the code cache, while inserting instrumentation at the specified points.

Dyninst [7], Gilk [37], KernInst [42] and DTrace [2] are examples of instrumentation systems that rely on code splicing to apply the instrumentation. Pin [31] and Valgrind [34] are systems that rely on the recompilation at run-time strategy to perform instrumentation.

#### 2.1.4 Security

Run-time systems are gaining acceptance as the vehicle of delivering security against malicious code execution. All security systems, regardless of whether they are dynamic or static in nature, are bound to impose execution overhead on the application being monitored. However, due to the fundamental design of run-time systems, dynamic security systems can adapt their monitoring mechanisms to be either active or inactive to limit performance degradation. Furthermore, applying run-time system based security has the added benefit that modifications are not required to the host environment. Most successful tools [8, 15, 9, 36] require a customized environment to operate.

#### 2.2 Fundamental barriers

The usefulness of run-time code transformation systems is apparent from the applications presented in the previous section. Yet, these dynamic code transformation systems are not prevalent in everyday systems. The lack of enthusiasm in realizing their potential is because these systems face numerous challenges.

Low overhead: All run-time systems experience overhead since their execution is interleaved with the execution of the application itself. To keep the overhead minimal run-time systems are required to collect dynamic information, as well as perform lowoverhead optimizations.

*Hot code detection:* To keep the overhead low enough, the optimizations performed, or the information collected, must be applied to those sections of application code that are vital for performance and carry out optimizations accordingly.

*Efficient optimizations:* Upon having identified the hot code, these systems need to carry out optimizations and apply them to the execution run. This step involves two critical aspects: (1) time to optimize and (2) the strength of the optimizations. Both of them are closely tied together; with an increased amount of time, more efficient code can be generated. However, increased time for analysis and optimization can hurt performance if a significant amount of time is not spent executing the optimized code sequences to make up for the time lost generating the sequences. This balance is hard to approximate without information such as the average lifetime of the program.

The work in this thesis aims at addressing the current barriers to state of the art JIT-based dynamic code transformation systems by specifically targeting their *low overhead* issue. The following section explains the framework utilized to study the issue.

# 2.3 Framework used to delineate and address the fundamental barrier

All the work presented in this thesis has been done using Pin [31]. Pin is a JITbased instrumentation engine that supports binary introspection on the IA32, EM64T, IPF and XScale platforms via the use of Pin Tools that export a rich user interface. Without applying instrumentation, the system can be viewed as a native-to-native binary translator. Pin performs various optimizations such as code caching, trace linking, inlining, register allocation and liveness analysis on the generated code to minimize the overhead incurred at run-time.

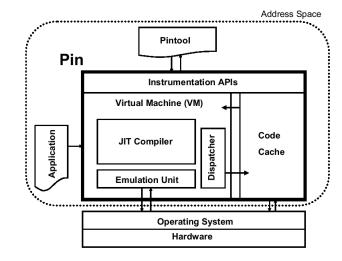

The system is illustrated in Figure 2.2. The core of the system is the Virtual Machine (VM). The VM works by injecting itself into the address space of the application being introspected, thereafter becoming a part of the application. It is not considered a separate process by the host operating system. The system does not execute any instructions out of the original application. Rather it utilizes the JIT compiler to recompile the application dynamically into the code cache. The recompilation occurs in small units of compilation called a *trace*, which is comprised of dynamic basic blocks. The motivation for doing so is explained in Section 3.2.1. Once the compilation is complete for that unit, control is transferred by the dispatcher to the code/translation cache, where the execution of the compiled unit occurs. If an execution path has not yet been previously visited and is about to be executed, control is transferred over to the virtual machine first, which generates the path. Once generated, subsequent executions of that path no longer invoke the VM. Instead, control is directly transferred to the target. An emulation module in the VM exists to assist with corner cases such as handling system calls.

Though Pin supports various platforms, this work focuses only on the IA32 platform. Data about application behavior is gathered using Pin Tools. Run-time system

Figure 2.2: Overview of the run-time system utilized as the evaluation framework.

behavior is also evaluated using the Pin infrastructure.

Of all the available run-time systems, Pin is chosen as the subject of evaluation since it is widely used both by industry and academia. Furthermore, it is currently looked upon as the state of the art run-time code transformation system in the domain of run-time binary instrumentation. Since its fundamental design resembles a general code transformation system, any conclusions drawn based on this system are fairly accurate and representative of other run-time code transformation systems. When evaluating run-time system characteristics, no instrumentation is applied unless stated otherwise. All experiments were performed on a system that hosted an Intel 1.7GHz microprocessor with 1GB main memory running the RedHat 7.0 Linux distribution unless explicitly stated.

#### Chapter 3

#### Challenges faced by state of the art run-time transformation systems

The fundamental barrier to run-time code transformation systems is the overhead incurred during execution. The slow-down incurred by applications running under a runtime system stems primarily from the transformation cost and the performance of the translated code.

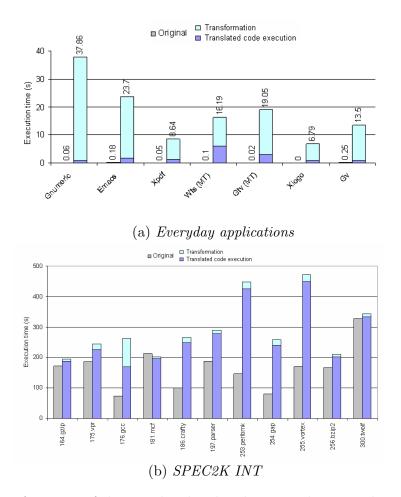

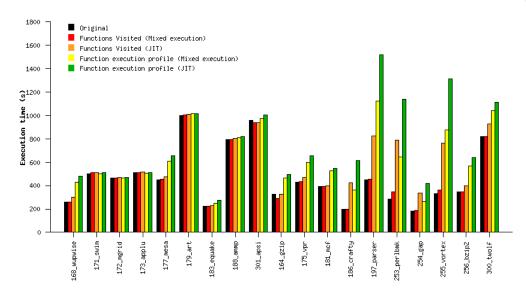

Transformation cost: In a JIT-based run-time system, original code is recompiled. This process incurs a certain amount of overhead. Figure 3.1 (a) compares the distribution of the time spent generating/recompiling the code versus executing it for the startup phase of graphic applications. The transformation and translation overheads are stacked on top of each other to illustrate the ratios of where time is being spent. The original startup times are less than a second for all the applications. However, under the run-time system, the applications experience several magnitudes of slow-down. The performance penalty is between 40x to 400x. A significant amount of time is spent transforming the code. When so much time is spent transforming code, even a faster JIT compiler will not be able to overcome this transformation overhead because the code consists of paths that are executed infrequently.

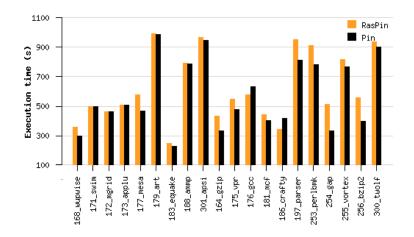

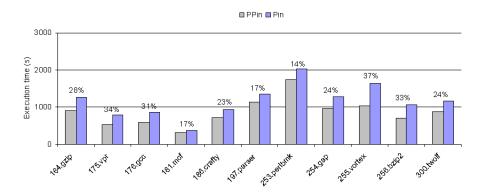

Translated code performance: This overhead is a result of the performance of the code generated by the run-time system. Figure 3.1 (b) compares the performance of the SPEC2K INT benchmarks against the performance of its translated counterpart. Once again, the run-time system transformation and translation overheads are stacked on top

Figure 3.1: Performance of the translated code relative to the original program. Execution time bars of the application running under the run-time system are stacked to show the distribution of the time spent generating the translated code versus executing the translated code.

of each other to illustrate the ratios of where time is being spent. Only SPEC2K INT benchmarks are shown since the applications contain fairly complex control flow relative to the SPEC2K FP benchmarks. The floating point benchmarks experience negligible overheads. From observing the data, it is seen that the overheads vary significantly from one application to another. In applications like 181.mcf and 300.twolf the overhead is tolerable. In others, like 176.gcc, 186.crafty, 253.perlbmk and 255.vortex, the slow-down experienced is over 2x.

Figure 3.1 confirms that both the transformation and translation overheads are

significant and need to be addressed. In the following sections, the transformation and translation costs are broken down to explain their origins. The overheads are explained in relation to the design of run-time systems and the behavior of applications. Following that, Section 3.3 takes a more holistic approach to the source of these problems. It demonstrates the impact of compilers and machine resources on run-time system performance.

#### **3.1** Transformation cost

The first form of overhead is determined by the run-time compilation steps and the amount of code that requires run-time compilation. The cost varies based on the execution characteristics of the application. Programs with large footprints, such as 176.gcc, tend to stress the infrastructure more heavily than their counterparts like 181.mcf, 164.gzip and 256.bzip. The latter have relatively smaller code sizes (smaller footprint) and fewer executed unique paths through code (less control intensive).

#### 3.1.1 Start-up (initialization) transformation overhead

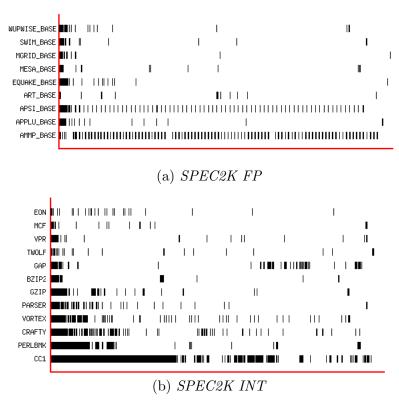

Figure 3.2 shows the usage of the Pin binary transformation infrastructure by the SPEC2K benchmark suite. They are sorted in ascending order based on how aggressively they utilized the infrastructure. The x-axis represents time while the y-axis corresponds to a unique benchmark. Therefore, a vertical line on the graph corresponds to a service request from the run-time system to either generate a new code sequence or to emulate a selective system call. At this point, the application is making no progress since the run-time system is executing and time is being spent in the Virtual Machine (VM). Space between two lines implies the application is making progress and time is being spent in the code cache. From observing the figure, specifically the SPEC2K INT benchmarks, it is evident that demands on the run-time system vary drastically from one application to another.

Figure 3.2: Time spent in the run-time code transformation system while executing the SPEC2K benchmark suite. Every black line represents the compilation of a new code sequences. Space between adjacent black lines indicates time being spent in already compiled code paths.

Benchmark 176.gcc while running under the run-time system experiences significant slow-down of approximately 3x. This is because the benchmark has a very large footprint with minimal code reuse. Therefore, a significant amount of time is spent by the run-time system compiling new code paths. Only near the end of each application run is the majority of the time spent executing the translated application.

Repeatedly invoking the code transformation system degrades performance since the effects of invoking the system are similar to a process context switch from the viewpoint of an operating system. Architectural resources like the cache, translation look-aside buffer, and branch target buffers, which exist to help application performance, are polluted every time the virtual machine is invoked. The insight gained from this data is that a benchmark with a large footprint will consume a substantial transformation

Figure 3.3: Average time between requests from the run-time system's virtual machine.

time. Also a significant amount of transformation time is spent on infrequently executed code.

Contrasting to benchmark 176.gcc is benchmark 181.mcf, which experiences no execution overhead while running under the run-time system as shown in Figure 3.1 (b). This benchmark performs well because it has a small working set that is quickly captured. As such, the run-time system is not invoked frequently. This is evident from Figure 3.2; the benchmark has fewer vertical lines. The same traits are also evident in benchmarks like 252.eon, as well as the entire SPEC2K FP suite. Such characteristics are ideal for run-time systems. The initial overhead incurred due to the run-time system is easily amortized by repeated executions of the already cached translated code sequences.

Data similar to Figure 3.2 is presented in Figure 3.3, which calculates the execution time divided by the number of code cache traces created for each application. The data indicates that the applications with reduced code footprints, such as 181.mcf, 197.parser, and 300.twolf all have longer time intervals between subsequent invocations of the run-time system. On the other hand, benchmark 176.gcc has a very short time period. Such a short period implies significant demands on the run-time system.

Figure 3.4: Cumulative percentage of the number of traces that dominate program execution.

#### 3.1.2 Infrequently executed code

Cold code, code executed once or a few times, is yet another source of transformation overhead for run-time systems. The execution of such code is challenging for run-time systems because they rely on amortizing the cost of the transformation overhead by repeated executions of the translated code sequences. Figure 3.4 shows the sorted distribution of code sequences generated by the run-time system to cover the execution of each program. Most of the execution time is spent in just a few traces, except in a few applications. On average, benchmarks spend the majority of execution time in fewer than 150 traces. Benchmark *176.gcc* has the largest code footprint, and therefore requires the most individual traces (greater than 500) to cover its entire execution. In fact, the run-time system used for evaluation, Pin, generates over 17,000 code sequences that contribute only about 1% to the complete execution. This is because much of the code is infrequently executed and also a result of code layout (explained in Section 3.2.1).

#### **3.1.3** Code transformation components

Figure 3.5 presents the components of the run-time system and their associated overheads when starting up graphic applications. These components describe the com-

Figure 3.5: Distribution of time spent in components of the run-time system.

plexity of each of the targeted application's ability to be transformed at run-time. By describing the components (stages) in detail, interesting points can be derived about issues with code transformation systems. The description of components are as follows: *Jitted application* is the time spent executing the code generated by the run-time system. *Instruction decoding* is the time to fetch instructions from the main applications text section. *Compilation* is the time to compile the fetched instruction stream from the native form into its corresponding translated form. *Code cache* is the time to perform trace linking optimizations. It also includes other services like those detailed in [17]. *Register allocation* accounts for the time to assign registers to the fetched code sequence so that register liveness properties are identical to the original code. *Miscellaneous* accounts for a series of other events in the system. These events include the allocation of basic blocks, setting up the state required to transition in and out of the dispatcher, the interception of system calls etc.

It can be seen in Figure 3.5 that for the applications shown, on average, less than 20% of the execution time is spent in *Jitted application*. All the others can be attributed to the time spent inside the run-time system transforming the code (i.e. compiling, allocating registers etc). On average, 25% of the time inside the run-time It is likely to be more efficient if this expensive optimization is applied in two phases. During the first phase, the system opts not to perform expensive register allocation on all the code sequences it generates. Rather, it utilizes the compiler generated register assignments. When the system itself requires registers to perform its task, it spills and fills the registers as required. This approach is likely to function well in comparison to the overhead resulting from this aggressive optimization. Once certain code regions are discovered as being *hot*, the system can regenerate them using expensive register allocation (the second phase). Since these code regions are likely to be executed for a significant amount of time, the time spent optimizing during the second phase can be amortized. This two pass technique is likely to work well with speculative fetching (described in Section 3.2.1) since a significant amount of time is not wasted applying this optimization on code that is never/rarely executed.

Taking a closer look at the miscellaneous costs associated with programs, the system call interception ensures that the run-time system is aware of things such as memory mapping, system calls etc. Some of these have to be emulated and cannot be directly executed. If not, the run-time system may lose control of the application. The emulator executes an instruction manually and lets the run-time system regain control immediately. As such, the application characteristics directly impact the distribution of the run-time system time. For instance, in the SPEC2K suite, programs with a high number of calls to memory management routines, such as 181.mcf demonstrate higher miscellaneous overhead. This is important to note since this time cannot generally be improved with better code transformation framework design. Rather, is the overhead experienced by ensuring that system calls are obeyed properly. Benchmark 176.gcc has more complex code, in terms of both functionality and control-flow; the register allocation time for generating code traces is much higher than the average of most other

applications.

In order to build effective run-time code transformation systems, designers must evaluate every component to ensure that they work efficiently. Figures 3.4 and 3.5 indicate that transformation overhead can be large. It can result from various things such as the infrequent execution of translated code sequences or the severe demands of an application on the miscellaneous services. Therefore, addressing the transformation overhead is critical to improving the performance of these systems.

#### **3.2** Translated code performance

While certain applications suffer from transformation overhead, others suffer from poor performance of the translated code. Translated code overhead is determined by a number of factors that include the characteristics of the original code, modifications applied to the code (optimization or instrumentation), and transformation artifacts for transparently maintaining the original application's functionality. In the absence of code optimization and instrumentation, the dynamic execution count of translated code may have significant overhead as detailed in the following sections.

#### 3.2.1 Code layout

Overhead can be added based on the layout of the translated code in memory since this determines the I-cache, translation look-aside buffer (TLB), and memory system performance. Most JIT-based run-time systems compile the application code in units, each referred to as a *trace*. A trace consists of a pre-defined number of conditional control flow instructions, a pre-defined number of fetched instructions or it is code selected due to its execution characteristics. If a trace is built without applying prior knowledge of the dynamic execution path of program, it can be said that the trace consists of a speculative instruction stream. This is so because the system cannot determine whether the instructions in the trace will all be executed or not.

Figure 3.6: Code duplication that results as a result of speculative fetching and trace formation.

Most dynamic code transformation systems speculatively fetch instructions into the compilation unit in order to minimize the overhead of being frequently invoked. Through speculative fetching the run-time systems hope to maximize the time spent executing the translated code. A trace is a single-entry, multiple-exit unit. Therefore, even if the source and target of a control flow instruction are in the same trace, the source cannot branch to the target basic block. A new trace must be generated beginning at the target. These units of compilation are utilized by most systems such as [3, 6, 31, 4].

Speculative fetching and the constraint of a single-entry, multiple-exit code sequence has a negative side effect, which is code duplication. This is illustrated in Figure 3.6. Trace 1 has basic blocks: A, B, C, D, and E. The conditional taken path of basic block A is basic block C. Since A and C are in the same trace, and C cannot be reached from A, a new trace beginning at C must be created. Because the principle of speculative fetching is applied, Trace 2, that begins with basic block C, speculatively fetches basic blocks D and E prior to reaching its trace termination condition. As a result of the speculative fetching, basic block C, D and E are duplicated in the code cache.

The concept of trace formation is akin to the concept of *superblocks* in the domain of static compiler optimization. However, the consequences of such code duplication

Figure 3.7: Percentage of all the translated application code utilized by the run-time system.

are quite different from its static counterpart. Code duplication in a run-time system implies more time to compile the code, as well as to execute it. The application makes no progress during the compilation process. Furthermore, duplication may also result in code sequences that never executed. The run-time system under evaluation, due to its speculative fetching, utilizes only 40% of the code it generates at run-time, as shown in Figure 3.7. Usage is shown for every reference input set; 164.gzip(1) refers to the first SPEC2K INT reference input data set followed by 164.gzip(2), which corresponds to the second input data set, etc. Another observation about the utilization of the code generated is the consistent behavior of applications regardless of the input data set. Consider benchmark 253.perlbmk, its cache utilization does not vary significantly over 33% despite the input data set. All benchmarks with multiple input data sets, 164.gzip, 176.gcc, 253.perlbmk, and 255.vortex, exhibit no variation in code utilization despite the input data set. This observation illustrates the effects of trace creation are independent of the input data set.

The result of speculative fetching is an increase in compilation time. Also, if

the branch out of basic block A is frequently taken, the result is worse architectural performance. No I-Cache locality will be exhibited since all instructions brought in following basic block A will never/rarely be utilized. If *Trace 2* is located elsewhere in memory, perhaps on a different physical page, the result may be an increase in the execution time due to potential increase in instruction TLB misses.

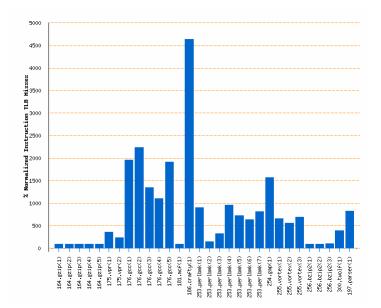

Figure 3.8 shows measurements made using the PAPI performance counters interface to count the increased number of instruction TLB misses experienced during the execution of an application under the control of a run-time system. Multiple inputs were used to evaluate the impact of the code transformation system on the performance of the TLB. Measurements indicate a severe number of additional instruction TLB misses for programs that exhibit a large number of service requests from virtual machine. At each virtual machine invocation, the application is deterred for long periods of time, waiting for the system to finish its task. By observing multiple inputs for several of the applications, it can be deemed that for some applications like 164.qzip, 255.vortex and 256.bzip2, run-time transformation disruption can be very consistent regardless of the input. Other benchmarks like 176.qcc and 253.perlbmk vary dramatically based on the input. As such, the design of modern run-time systems must be careful not to base design techniques on an aggregate value of the characteristics of all applications (e.g. average TLB miss rate). Instead, design decisions need to be evaluated in response to the application behavior based on varying the input data sets, and by comprehending the behavior of an application under a run-time system.

#### **3.2.2** Varying branch target instructions

Code that includes branches with varying targets requires special handling under a run-time system. Figure 3.9 illustrates how varying branch target instructions are handled in Pin. The system utilizes a virtual register, *indirectReg*, to resolve indirect branch targets at run-time. The original instruction, 0x805494b RET is translated into two in-

Figure 3.8: Percentage increase in instruction TLB misses when running the applications under the control of the run-time system.

structions: (1) a POP %indirectReg instruction to move the return target from the stack into the virtual register followed by (2) an unconditional branch, JMP 0x78000000, to the first translated return target trace. RET instructions can have multiple return sites, as such, the run-time system must make sure that control is transferred to the correct translated return target. To verify this a check is performed at the entry point of all return target traces. For example, the first three of a return target trace instructions starting at address 0x78000000 verify if the return site is address 0x8054900. If not, control is transferred to another return target trace beginning at address 0x78002000. If the current return target does not match any of the previously generated traces, the run-time system is invoked to generate a new return trace. The new trace is address 0x805494b. This approach is different from other systems; for instance, the virtual machine is invoked if the first prediction fails (e.g. DynamoRIO [6]).

In the presented approach, if the varying branch target instructions have numer-

Figure 3.9: Indirect branch predictions.

ous sites they can return to, the list sizes are likely to get large. Long lists are bad for performance; they will consume significant amounts of time to locate the trace that corresponds to the target. If the traces are located across different physical pages, performance may be degraded due to the poor performance of the I-Cache and the I-TLB.

# 3.2.3 Maintaining application transparency

Most run-time systems implement complex optimizations to ensure that the application being monitored does not alter execution because of the presence of the system. These optimizations come at a price, an increase in the execution overhead.

The run-time system used for evaluation, applies an optimization called *stack-switching*. In this optimization, the system ensures that it does not use the application stack for its own use. This is important to ensure application correctness. For example, certain applications access data beyond the top of the stack pointer. And if the run-time system places its own data on the top of the stack, it is possible to break the program.

While putting data on top of the stack is a matter of program correctness, the system itself must not make the bug visible. Therefore, optimizations like stackswitching are critical despite the overhead (stackswitching results in  $\sim 33\%$  execution overhead). Other optimizations exist that run-time systems implement to enforce transparency (e.g. system call emulation).

#### **3.3** Execution environment effects on run-time systems

Transformation and translation overheads explained thus far are from the perspective of application characteristics and how they relate to run-time system design. Another perspective on the challenges faced by run-time systems is the execution environment. Understanding the host environment of a run-time system can help us understand how to benefit from the potential of these systems. Code transformation and translated code performance can vary significantly based on the environment. Elements of the environment include the compiler used to generate the binaries, the optimizations applied or even architectural features of the machine. The current model of binary generation and delivery needs to be adapted in the future to facilitate the widespread use of these systems. The following sections illustrate that there exists a dire need for us to re-think the traditional model. The sections also make a brief point or two on how the current models can be adapted to cater for these systems.

#### 3.3.1 Compiler vendors

Compiler makers like *Gnu* and *Intel* try to out perform each other by generating efficient binaries. To achieve good performance their binaries are put through various levels of optimization. And once shipped to customers, the binaries are commonly referred to by their parent compiler and the optimization level applied during their generation (e.g. *Gcc 3.2.2* using -O3 flags). The actual set of optimizations applied at a given optimization level may vary from one compiler to another. As such, it is

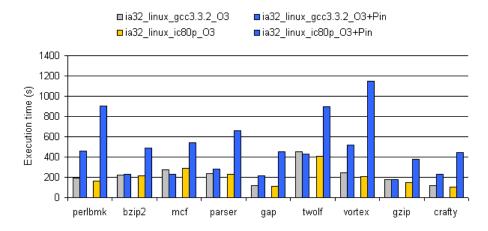

Figure 3.10: Performance impact based on the compiler used to generate the binaries.

important to understand the performance variation of an application under a run-time system when it is generated by different compilers at the same level of optimization.

Figure 3.10 compares the execution time of binaries generated by different compilers with and without a run-time system. The binaries were compiled using the Gcc3.3.2 and Icc 8.0 compilers using level 3 optimizations. Each application has four bars that are grouped into two sets. The first set corresponds to Gcc compiled binaries. Of the two bars in the first set, the first corresponds to the execution time of the application running by itself. The second corresponds to the execution time under the run-time system. Correspondingly, the next set of two bars reflect the execution time of binaries generated using the Icc compiler running with and without the run-time system.

Running without the run-time system, the original *Icc* binaries perform slightly better than those generated by the *Gcc* compiler. Contrasting to this are the execution times when the applications are running under the control of the run-time system. The times vary significantly between the two compilers. The run-time system performs significantly better on the *Gcc* compiled binaries. Also, when benchmark *181.mcf*, generated by the *Gcc* compiler, is run under the run-time system, it consistently yields better performance than the original run. The application benefits because of good code layout.

All the *Icc* generated binaries require more compilation and register allocation time. These binaries contain more control flow compared to the *Gcc* compiled binaries. The *Icc* binaries also have more indirect branch instructions. Such instructions require special handling as explained in Section 3.2.2. Figure 3.10 shows that product compilers compete and evaluate their system performance against one another. As such, with run-time systems moving into mainstream computing environments, it is critical that compiler vendors evaluate the performance of their binaries under these systems.

# 3.3.2 Compiler optimizations

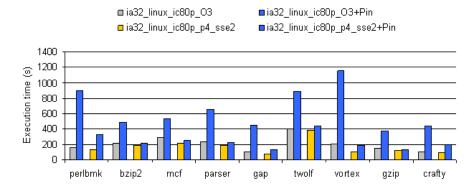

Binary optimizations applied by compilers can affect the performance of a code transformation system. Two sets of binaries were generated using the *Icc 8.0* compiler under varying levels of optimization. Each application contains four bars that are grouped into two sets as shown in Figure 3.11. The first set corresponds to the execution time of the application compiled using the standard O3 flags running with and without the code transformation system. The second set corresponds to the binaries compiled using more aggressive, as well as chipset specific optimizations.

There is not much gain in performance between the two sets of binaries when they are run by themselves without the transformation system. However, the aggressive optimizations have a dramatic performance improvement on the run-time system as shown in Figure 3.11. The results indicate that the system overhead is reduced on average by nearly 50%, and dramatically reduced in cases of 255.vortex, 253.perlbmk, and 197.parser.

To understand this behavior, vortex, compiled using the standard O3 flags is analyzed. It has the worst performance of all benchmarks compiled using the standard O3 flags. 255.vortex has subroutines that are heavily invoked from numerous callsites. A subroutine CALL instruction almost always terminates with the execution of a RET

Figure 3.11: Effects of compiler optimizations on the performance of code transformation and translated code execution time.

instruction. Of all the indirect branches executed, the benchmark executes  $\sim 94\%$  RET instructions. Furthermore, the number of unique callsites to a single function is as high as 233. And as explained in Section 3.2.2, varying branch target instruction requires special handling in a run-time system and are the source of significant overheads.

A solution to mitigate the performance overhead resulting from the numerous RET instructions is the aggressive inlining of subroutine calls. Aggressive inlining eliminates the CALL and RET instructions along with other prologue and epilogue instructions. This reduces the number of indirect RET instructions to handle. As a result, performance of benchmark *255.vortex* improves by nearly 50%. Therefore, it is extremely critical that the static compiler is aware of the effects of its optimizations on a dynamic code transformation system. Such an awareness can help keep the overheads minimal.

# 3.3.3 Compiler consequences on dynamic optimization

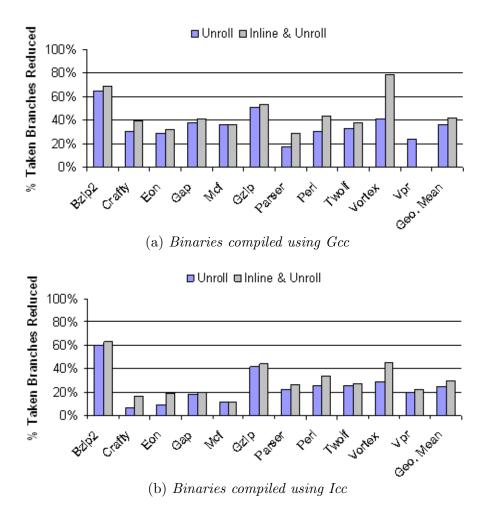

Run-time systems are being explored to boost the application performance by exploiting execution characteristics [3, 6, 11, 29]. However, it is critical to first understand the scope of dynamic optimization as it stands in todays computing environment (i.e. potential for run-time specific optimizations). Figure 3.12 shows the ability of a Pin-based code optimization system (known as the O-Pin framework) to perform dy-

Figure 3.12: Comparison of dynamic optimization (loop unrolling and inlining) on binaries generated using different compilers: (a) Gcc and (b) Intel (Icc).

namic loop unrolling and function inlining on translated code sequences. As illustrated in earlier sections, the compiler can directly impact the application behavior as observed by the code transformation system. For instance, the compiler may have already performed a large amount of optimization. If so, it is possible that the scope for run-time transformations is limited.

Figure 3.12 (a) shows the percent reduction in taken branches using dynamic loop unrolling and inlining on code originally generated using the  $Gcc \ 3.2.2$  compiler. While Figure 3.12 (b) show the same percent reduction for code compiled with the *Icc* 8.0 compiler. The *Gcc* compiler generated binaries achieve a 40% reduction in the number of taken branches, while the *Icc* compiler generated binaries achieve only 30% reduction in taken branches. The latter set of binaries exhibit relatively fewer opportunities for the run-time system because they have already been optimized using loop unrolling and inlining.

This leads to an interesting question: is it possible to inhibit potential run-time optimizations due to static code structuring techniques? The static compiler may be able to aid a run-time transformation system without generating code that assumes certain run-time behavior. Overall, the future of proposing any profile-based compilation is at question since the run-time system may be able to eliminate its need.

### **3.3.4** Machine resources

Microarchitectural features exist to help boost application performance. The L1/L2 cache, Branch Target Buffer (BTB), Trace Cache, Return Address Stack etc. are all such resources. The effectiveness of these resources is determined by the dynamic instruction stream of the application. For instance, the BTB's usefulness is mitigated if the dynamic instruction stream consists of a significant number of branch instructions. An excess of branch instructions (static count) can cause BTB thrashing. Consequently, it hinders the system from capturing the history pattern of certain branch instructions. As a result, more branch predictions are likely to be incorrect. This directly impacts the performance of the pipeline. Incorrectly predicted branch instructions flush the pipeline resulting in an increase of the execution time. Certain static compiler optimizations are aware of this and perform their task accordingly. Along those lines, the following sections present the overall impact of architecture resources on the performance of runtime systems.

Figure 3.13: Run-time system performance observed under different processor/system resources.

#### **3.3.4.1** Resource impacts

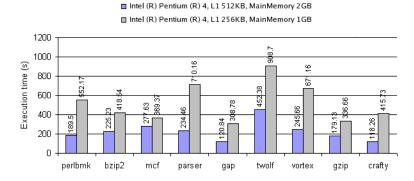

In order to evaluate the impact of machine resources on a run-time system, two systems were selected to evaluate SPEC2K INT benchmarks. By averaging the execution time across inputs, and comparing the difference between two systems, insight is gained about the operating characteristics of the code transformation system. The results are shown in Figure 3.13.

The presented results do not show the percentage relative to the improvement in the base. Rather, they highlight the performance improvement obtained to the run-time system given more resources. The two systems differ in processor speeds and on-chip cache capacity by a factor of two. The observed performance improvement is on average 60%. One of the largest improvements is seen in benchmark *255.vortex*. The benchmark is a memory intensive application [10] that suffers from cache limitations. This factor is directly attributable to the increase in processor resources. It experiences less interference with the code transformation system as a result of a larger cache (increase from 512KB to 1M level-2 cache).

Several run-time analysis and optimization techniques can be activated in a host system with larger architectural resources since the corresponding overheads can be mitigated. An interesting study is required to determine the exact limits to which dynamic code transformation systems can be stretched between processor generations.

# 3.3.4.2 Utilizing architectural features

Most modern processors (e.g. Pentium and Athlon) maintain an internal stack called the Return Address Stack (RAS) to help boost application performance. This technique is capable of improving performance by as much as 15% in programs that execute subroutine calls frequently [27]. This stack is updated every time a CALL or RET instruction is executed. When a CALL instruction is executed, the original application return target address is put on top of the return address prediction stack. The return target is also placed on top of the regular application stack; on the x86 architecture this is referred to via the **%esp** register. The execution of a RET instruction *pops* the top address off of the return address stack, as well as the regular stack. An instruction stream, beginning at the address on top of the return prediction stack, is fetched to keep the processor pipeline busy.

The RAS functionality, as explained above, is tied to the CALL and RET instructions. Most run-time systems modify these instructions into their run-time idiom form to ensure proper execution of the program in the presence of the run-time system. There are two fundamental issues associated with these modifications/translations. First, it imposes overhead due to the special handling required for RET instructions (explained in Section 3.2.2). Second, it inhibits the use of the RAS.